# Elettronica dei Sistemi Digitali e Laboratorio di Elettronica

Corso di Laurea in Informatica e Tecnologie Fisiche Innovative Anno Accademico 2008-2009 > Periodo didattico: I trimestre dal 22 Settembre al 29 Novembre 2007

➤ Aula lezioni di teoria : F4

➤ Laboratorio di Elettronica : F3

➤ Titolare del corso: dott. Mirco Andreotti

➤ Email: mandreot@fe.infn.it

➤Tel. Uff.: 0532/974328

➤ Studio: stanza Dip. Di Fisica C228

Orario: Mar 9:00 - 11:00 (aula F4) INFO + TFI

Mer 9:30 - 13:30 (Lab F3) INFO

Gio 9:00 – 13:00 (Lab F3) TFI

#### Testi consigliati:

- Stampe e/o fotocopie delle dispense (disponibili online all'indirizzo <a href="http://df.unife.it/u/mandreot">http://df.unife.it/u/mandreot</a> oppure dal sistema di gestione delle dispense dal sito UNIFE)

- ➤ P. Horowitz, W. Hill "The Art of Electronics", Cambridge University Press, New York (1980)

- R. Giometti, F. Frascari "Elettronica, La Logica", Calderini, Bologna (1990)

- ➤ J. Millman, "Circuiti e sistemi microelettronici", Bollati Boringhieri, Torino (1985)

#### Svolgimento del corso:

- > Lezioni teoriche con qualche avanzato elemento di matematica per un approccio approfondito all'algebra di Boole

- > lezioni di laboratorio pratico

- > lezioni di laboratorio con simulazione

- > progetto da realizzare in gruppo

#### Modalità d'esame:

- ➤ se presenze in laboratorio > 50%

- ➤ Test a risposta multipla per l'ammissione all'orale

- ➤ Orale sul progetto finale e programma del corso (il numero di domande varia da esame a esame)

- ➤ se presenze in laboratorio < 50%

- > Pratico + Test + Orale

- ➤ in appelli ufficiali

- > fuori appello, previo accordo con la commissione

#### Frequenza:

> non c'e' obbligo di frequenza

#### **Elettronica Digitale**

#### 1. Strumenti matematici per l'elettronica digitale

- ➤Introduzione alle grandezze fisiche che interessano l'elettronica

- ➤Introduzione ai sistemi elettronici digitali

- ➤ La logica dei sistemi elettronici digitali

- > Sistemi di numerazione

- ➤ Algebra di Boole + trattazione matematica matriciale

#### 2. Elettronica digitale combinatoria

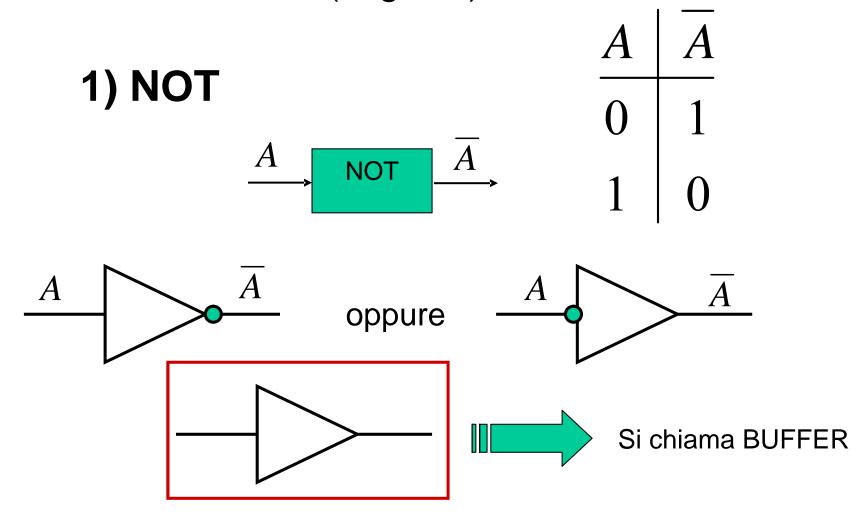

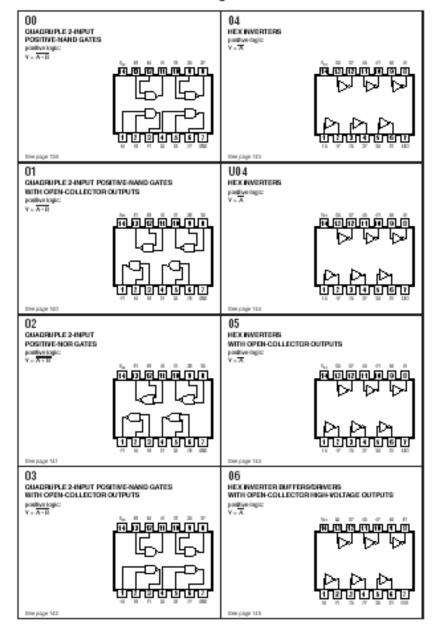

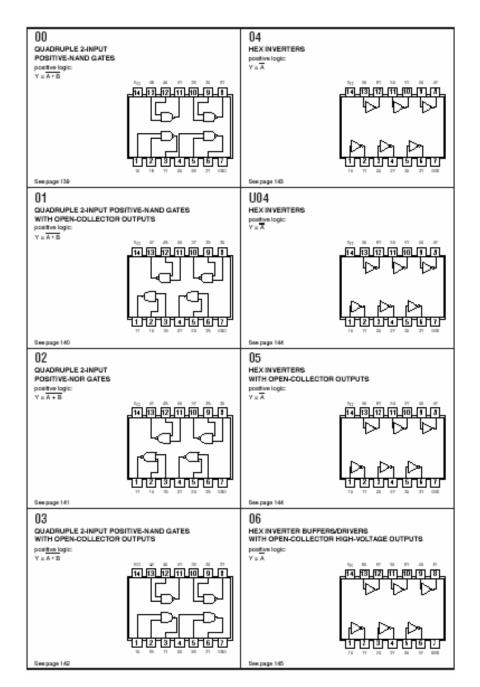

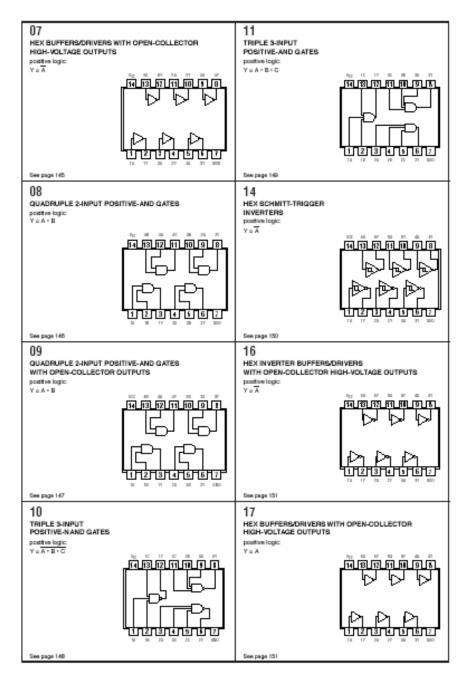

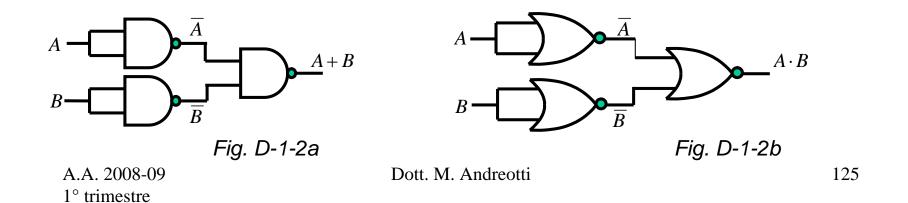

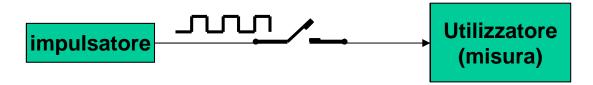

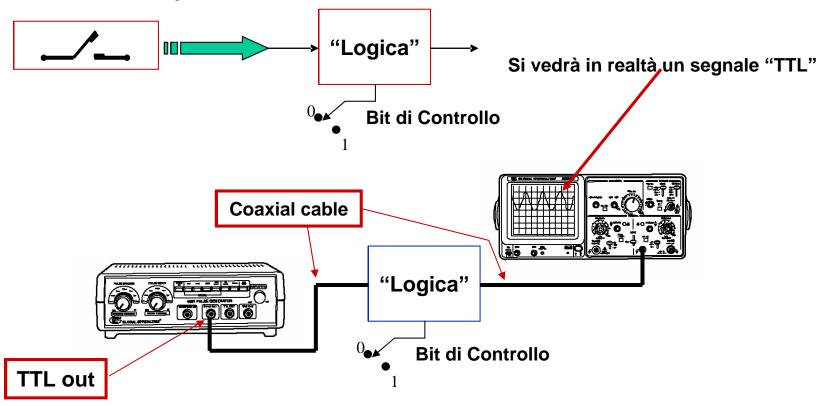

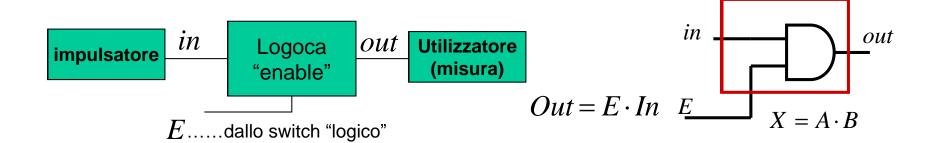

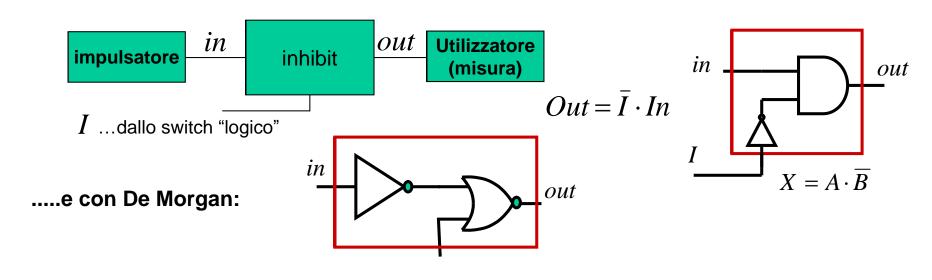

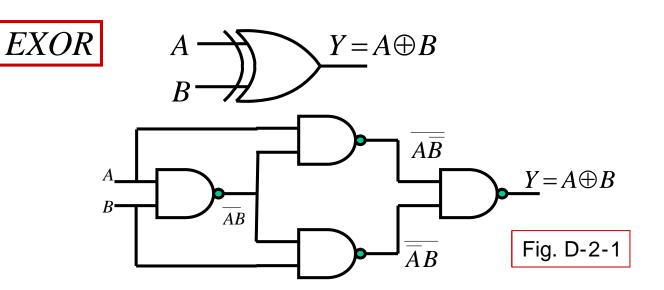

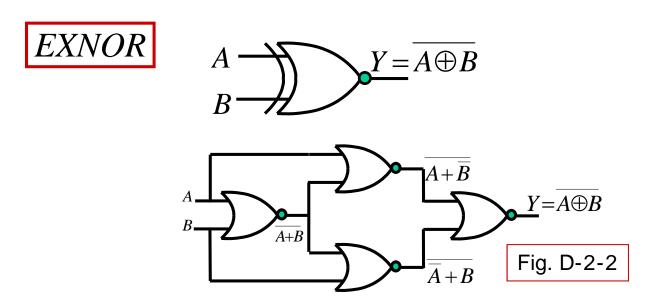

- ➤ Operatori elementari: porte logiche NOT, AND, OR, NAND, NOR, EXOR, EXNOR; porte con bit di abilitazione ed inibizione (ENABLE, INHIBIT); l'universalità delle porte logiche NAND e NOR.

- Cenni sui circuiti integrati: gruppi, famiglie e caratteristiche.

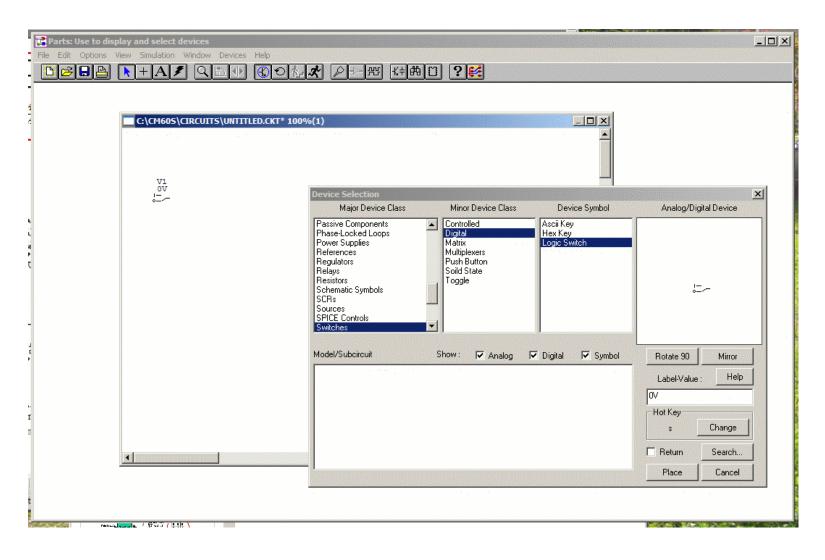

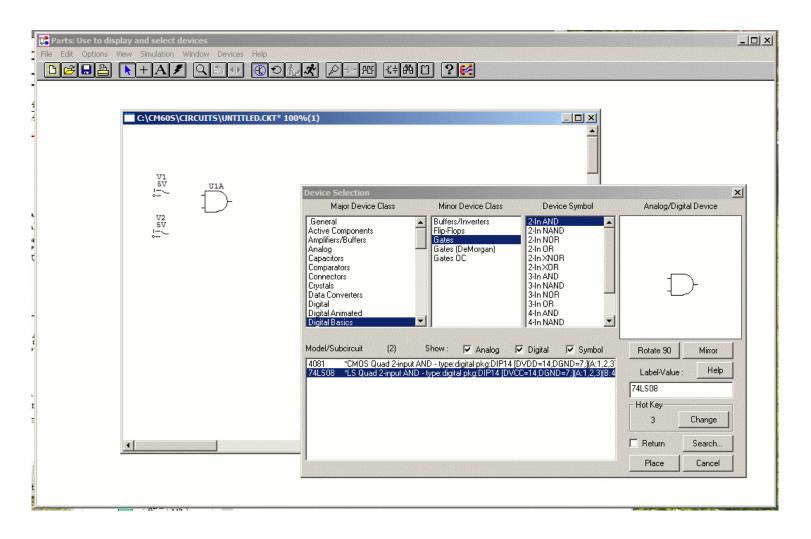

- > introduzione al simulatore circuitmaker

- > Studio di circuiti logici combinatori.

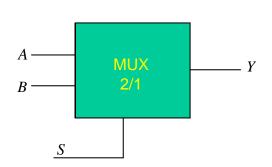

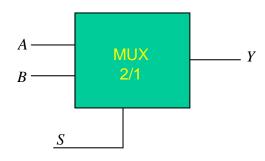

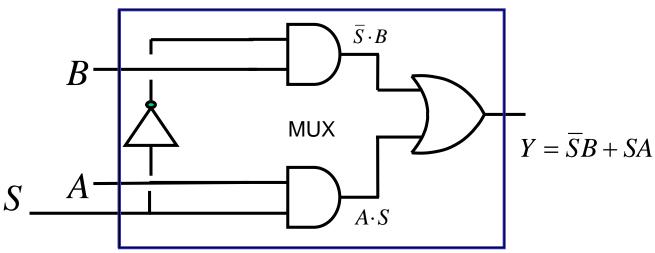

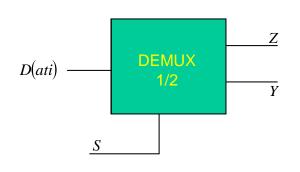

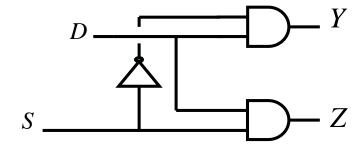

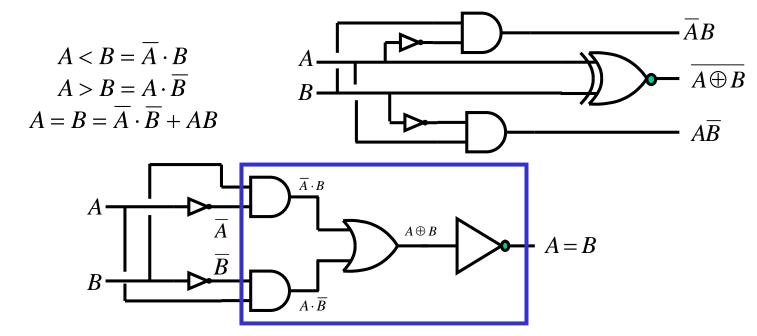

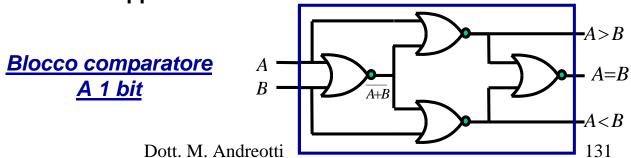

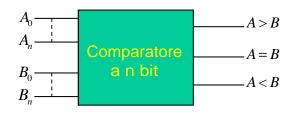

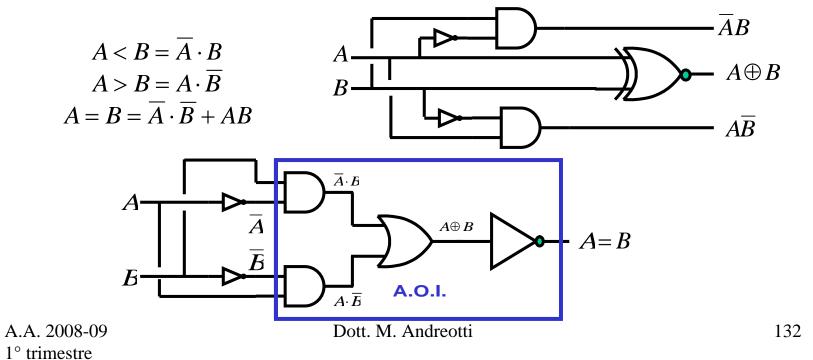

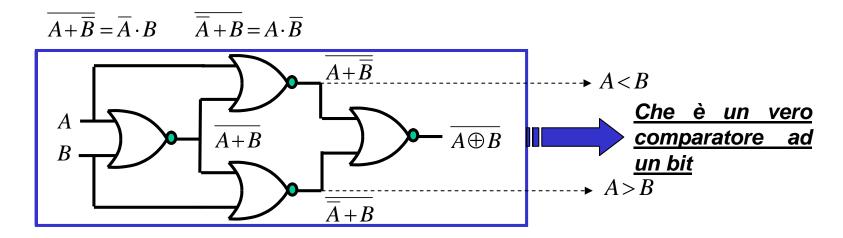

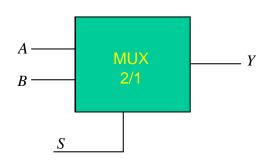

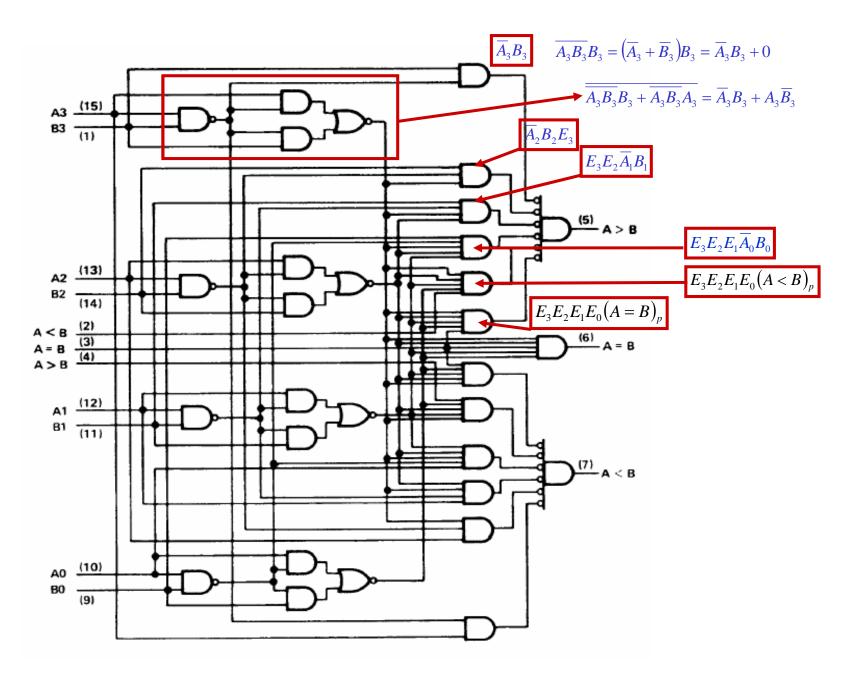

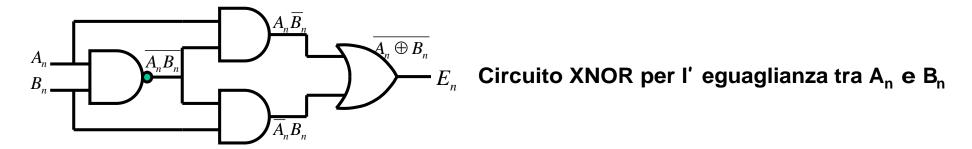

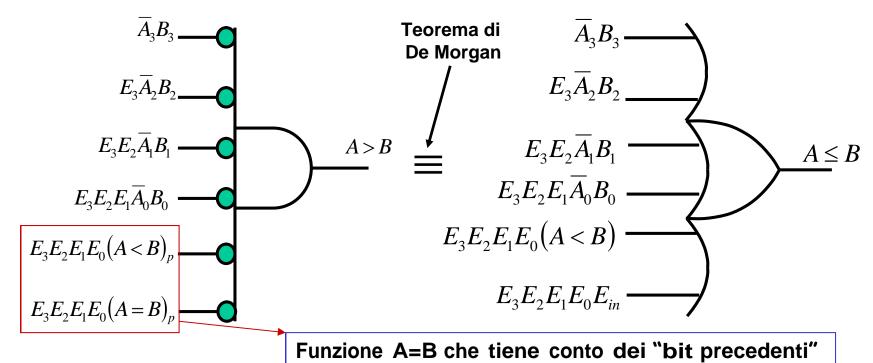

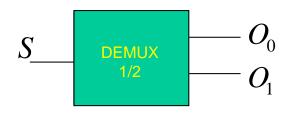

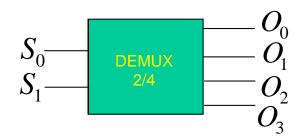

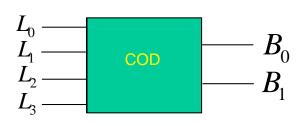

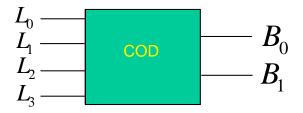

- Comparatori digitali, MUX, DEMUX

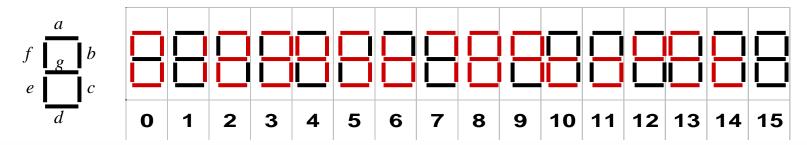

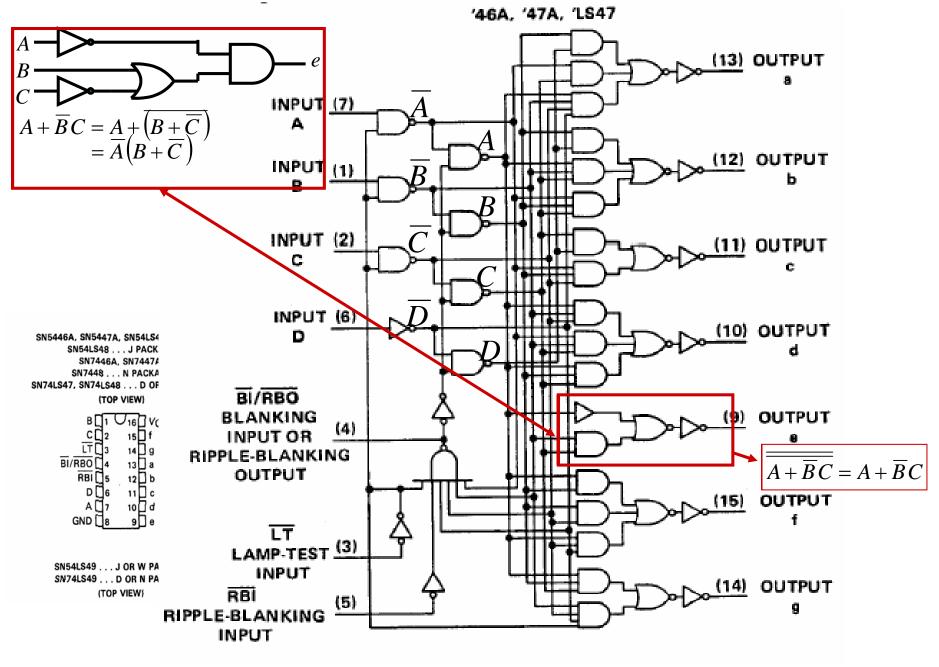

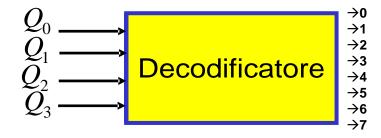

- ➤ Convertitore BCD 7 segmenti

#### **Elettronica Digitale**

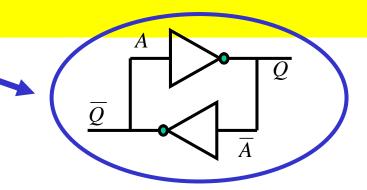

#### 3. Elettronica digitale sequenziale

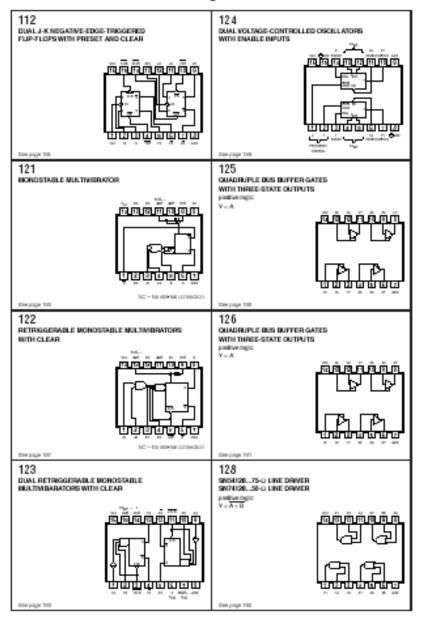

- ➤ Studio di circuiti logici sequenziali

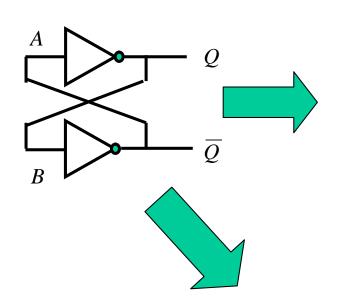

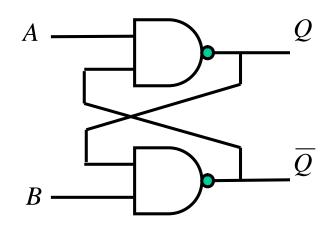

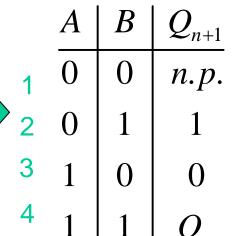

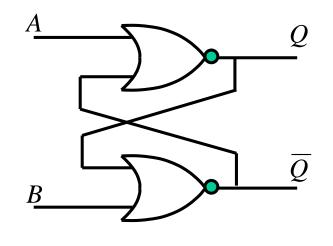

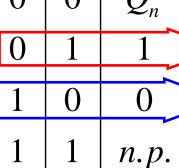

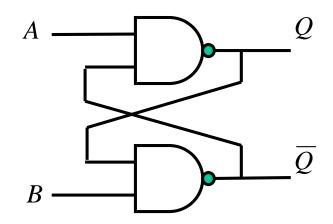

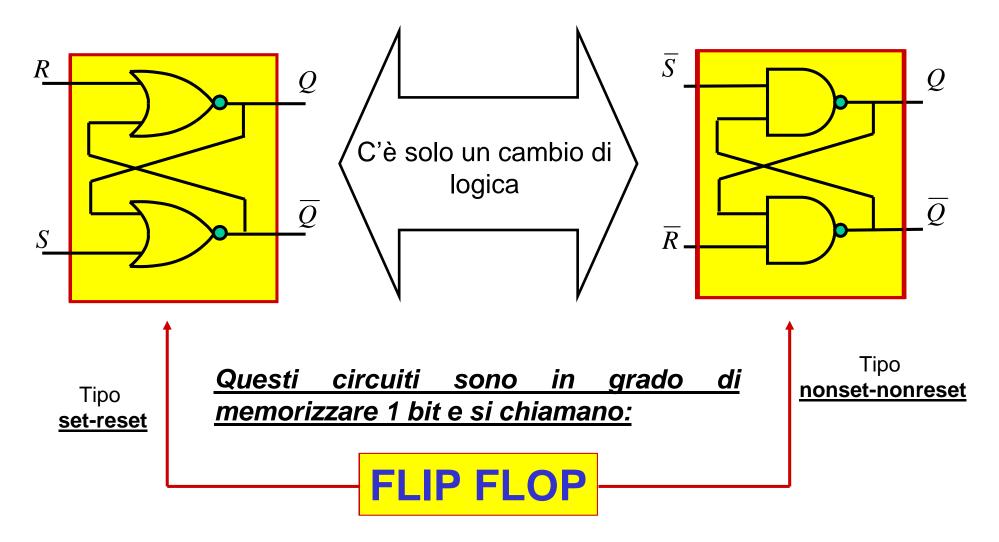

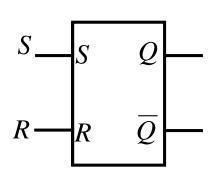

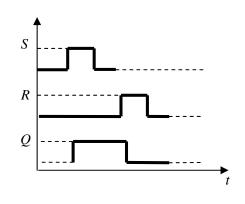

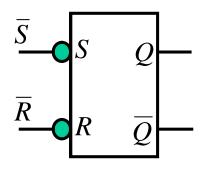

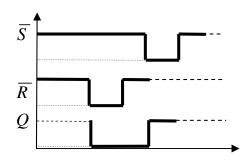

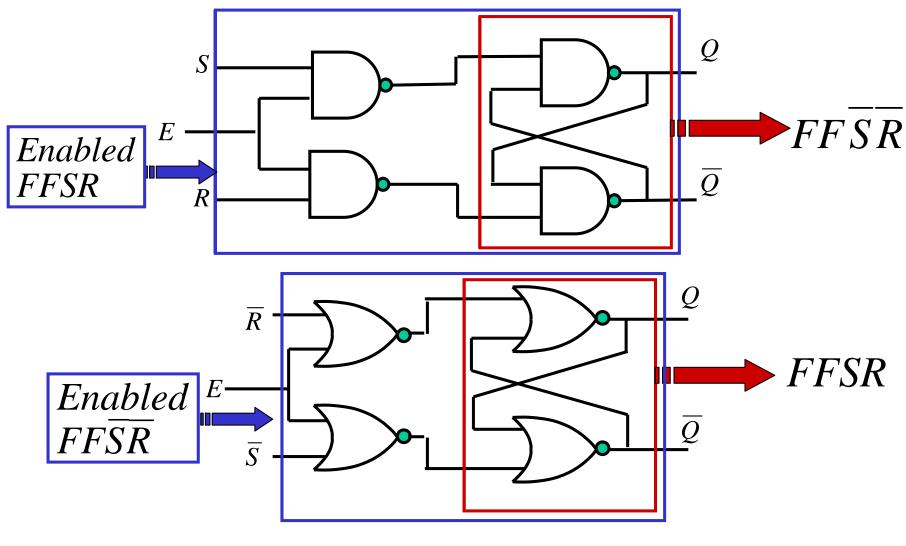

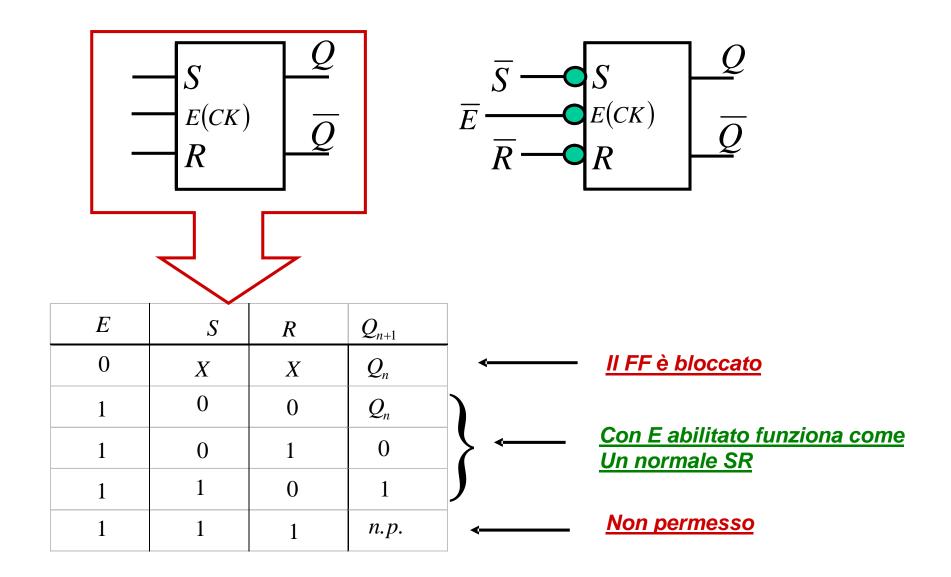

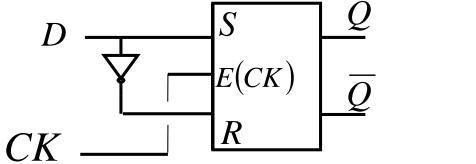

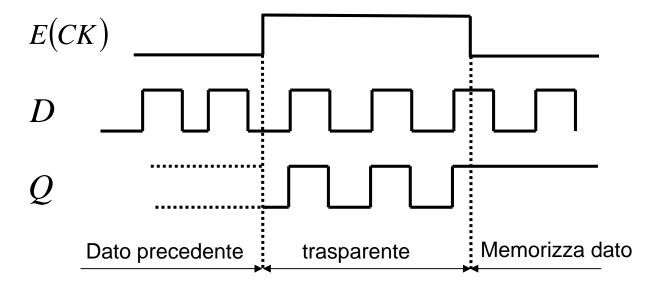

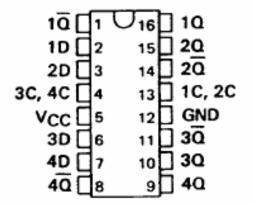

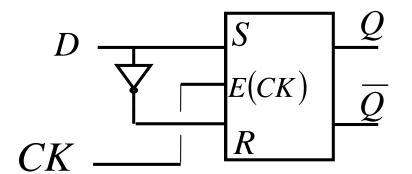

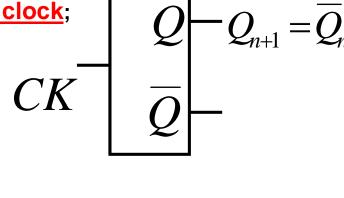

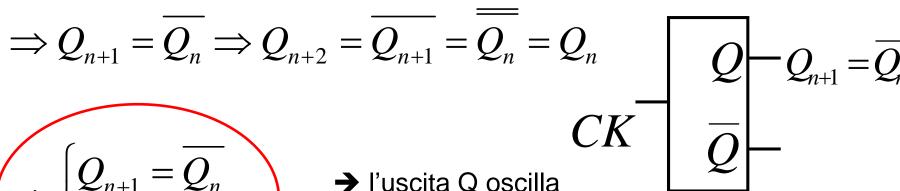

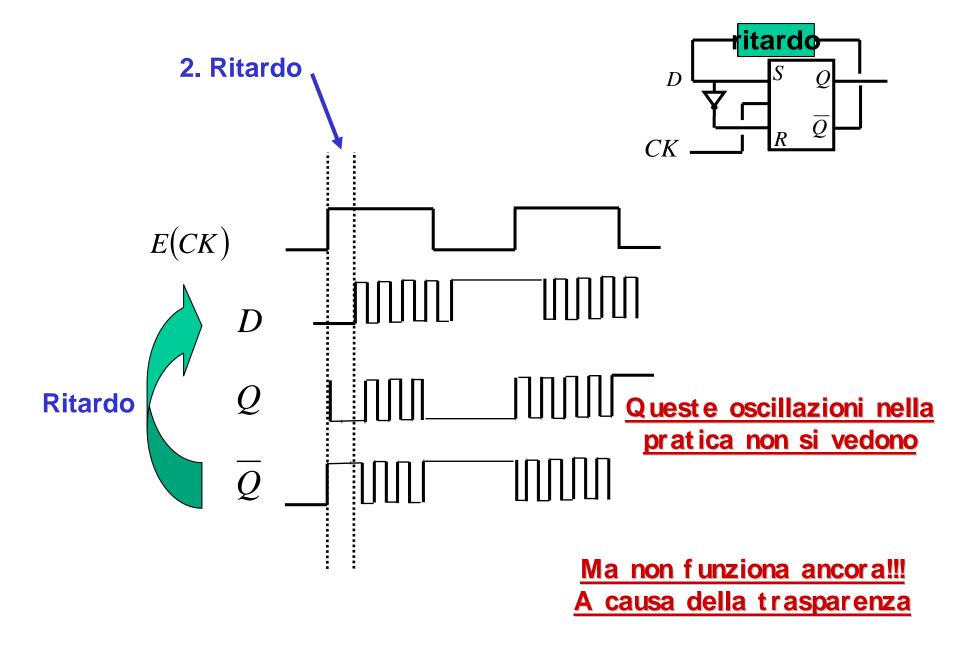

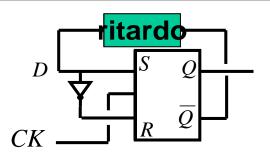

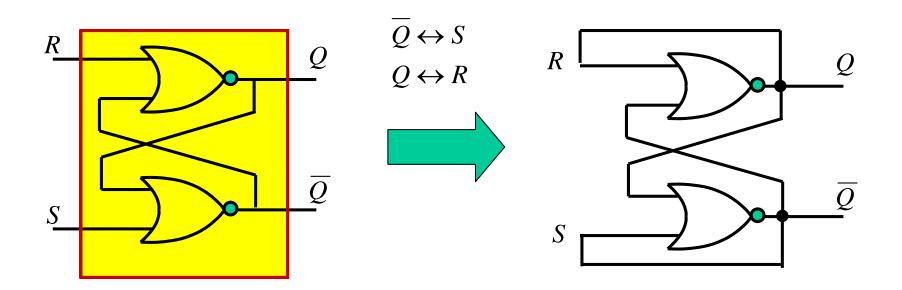

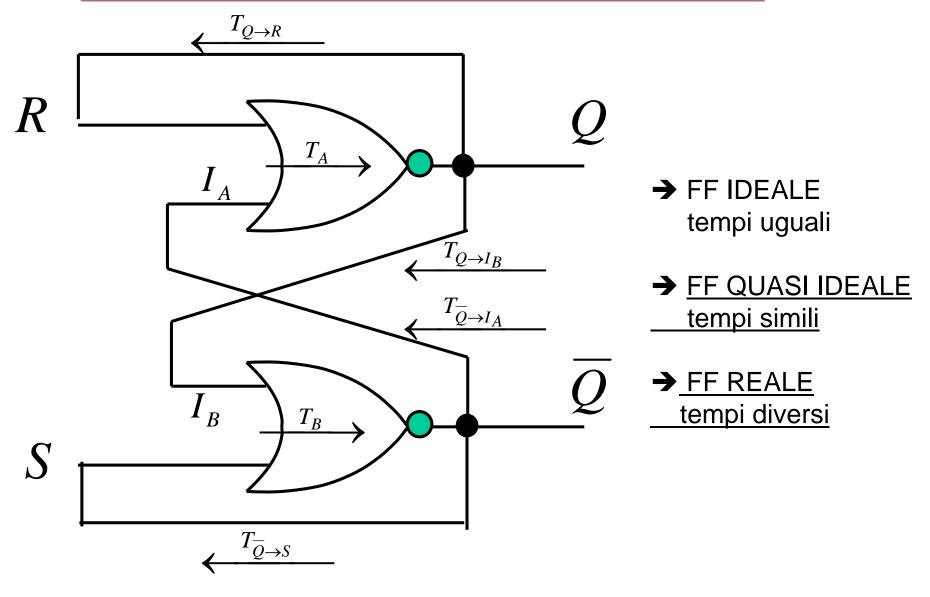

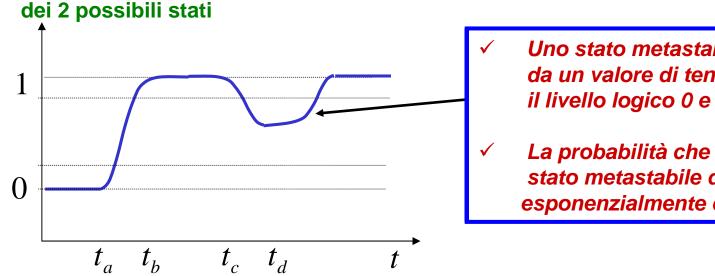

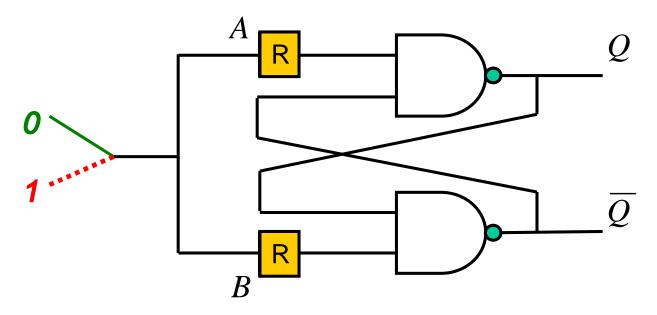

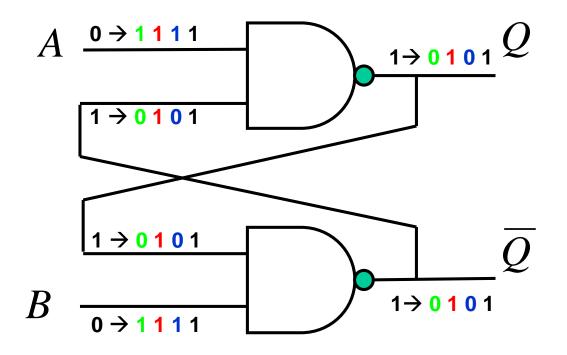

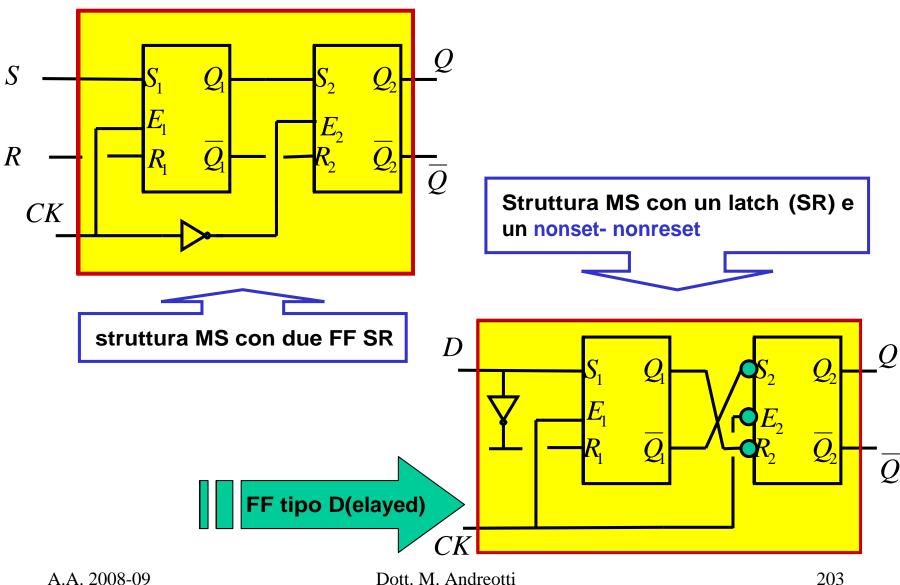

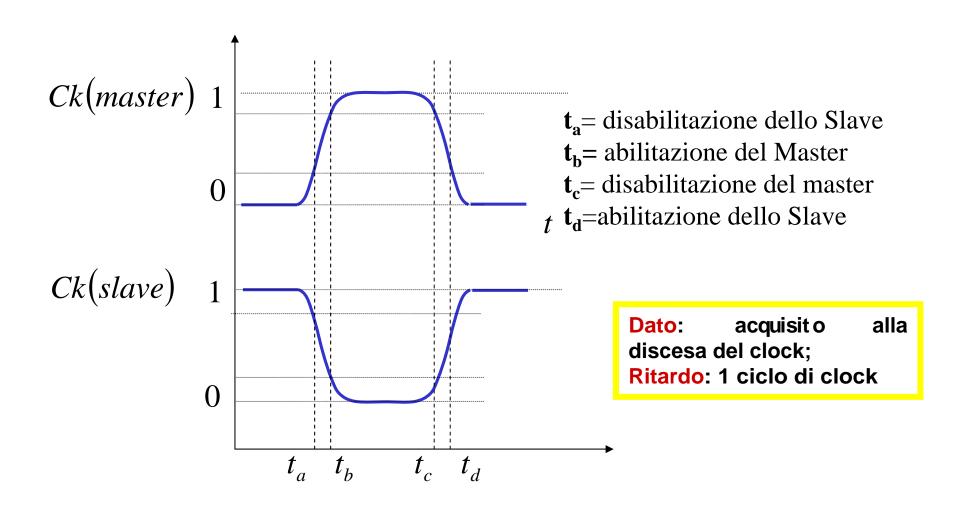

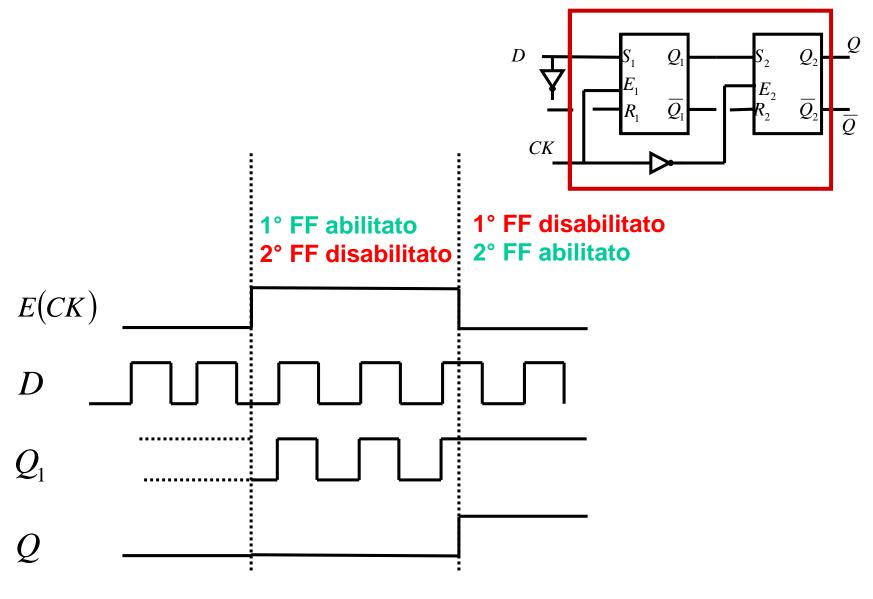

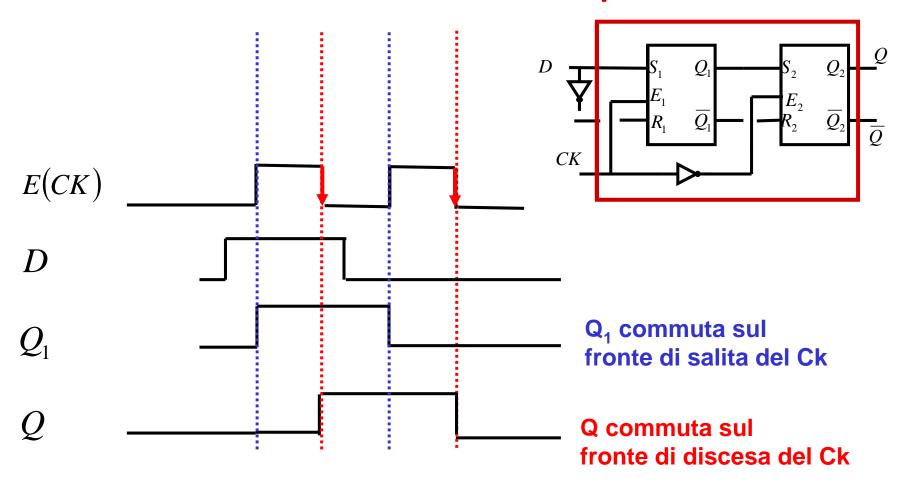

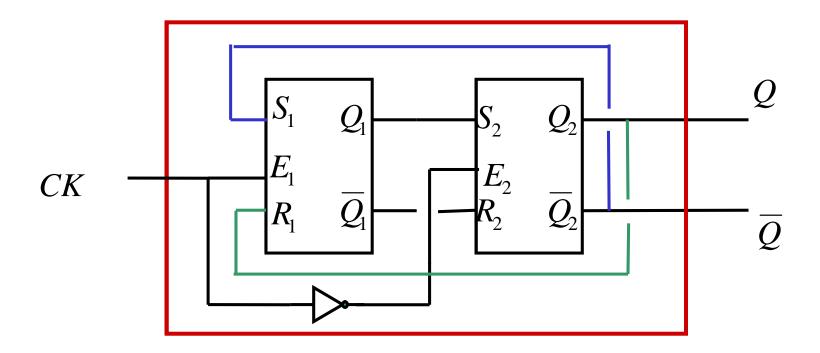

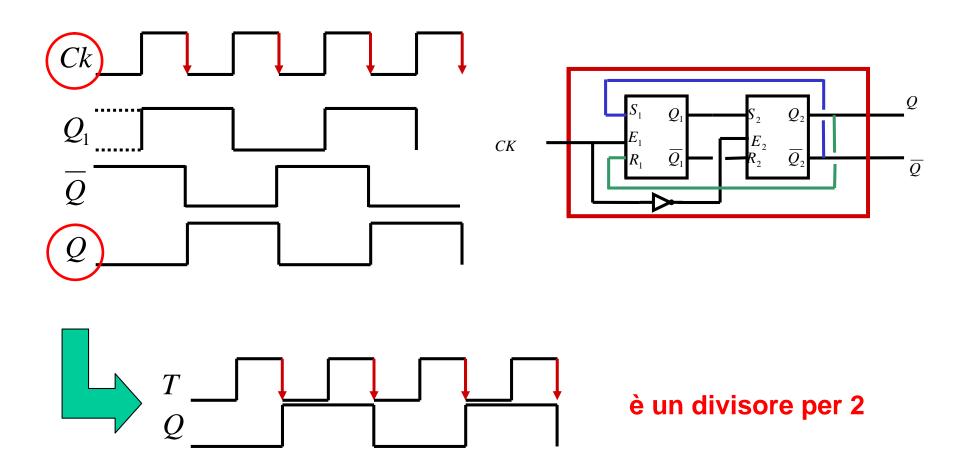

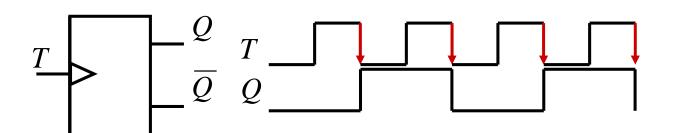

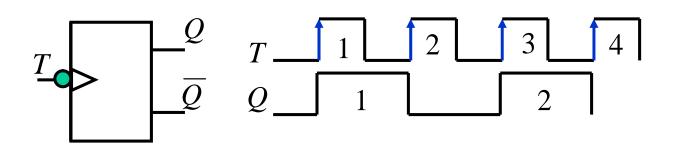

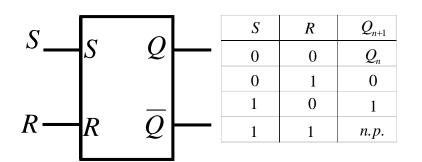

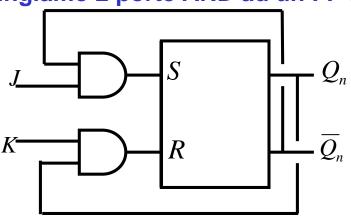

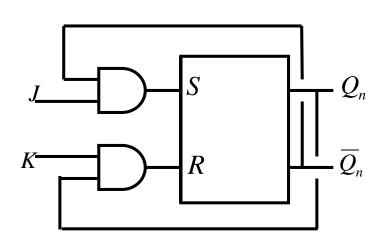

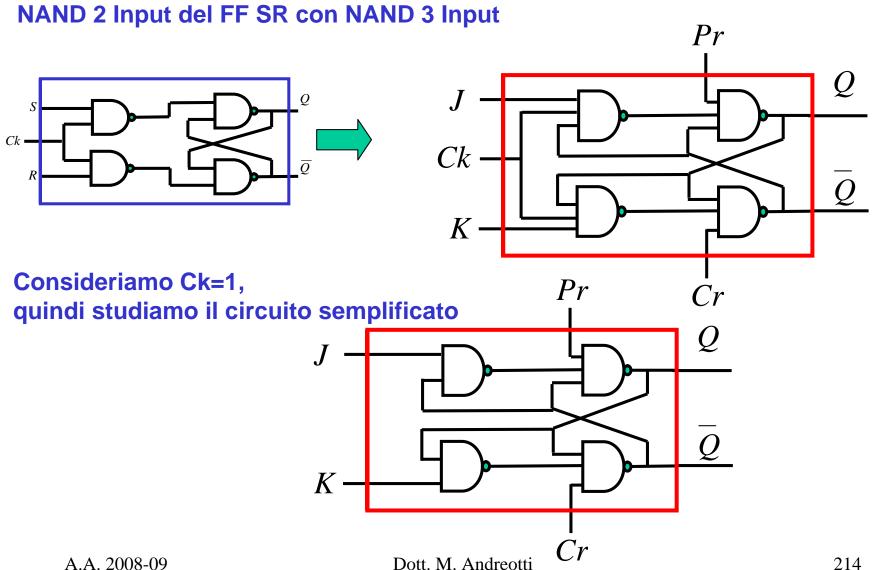

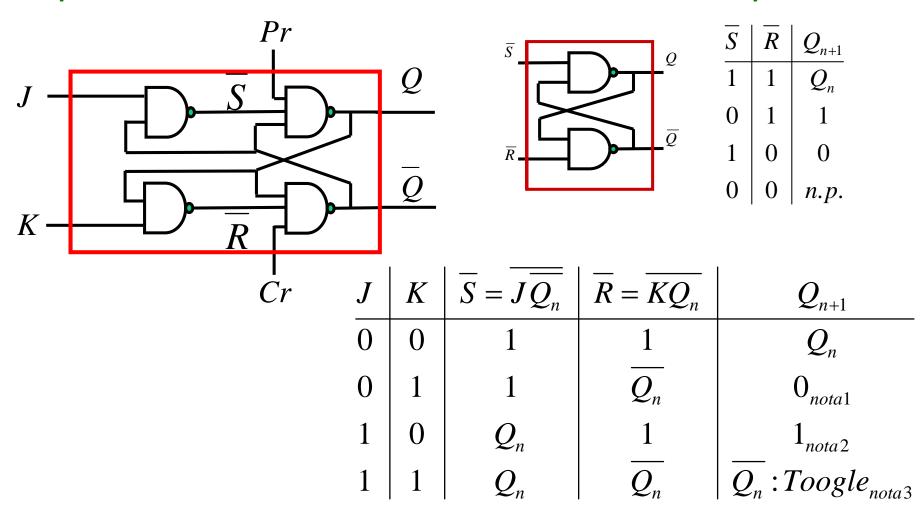

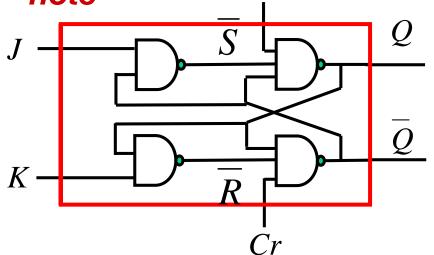

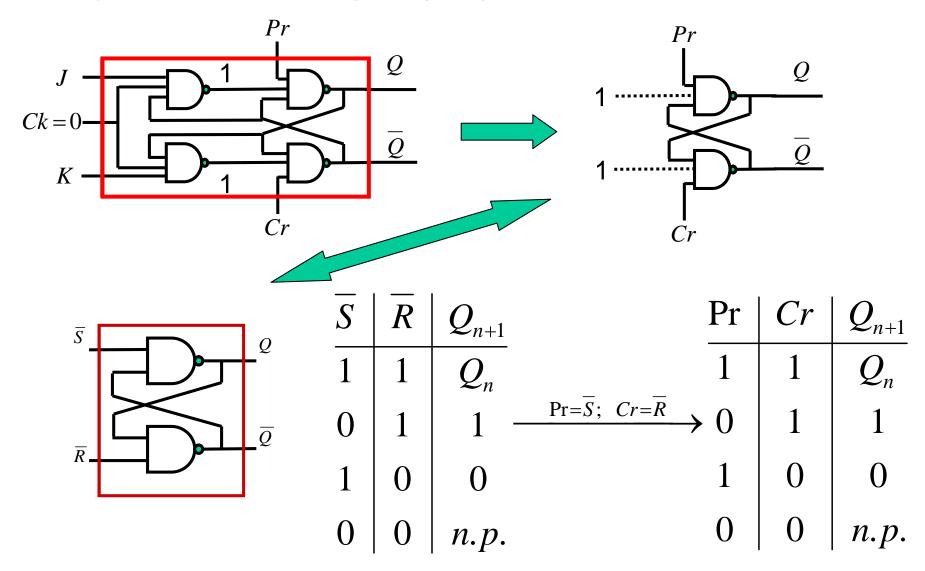

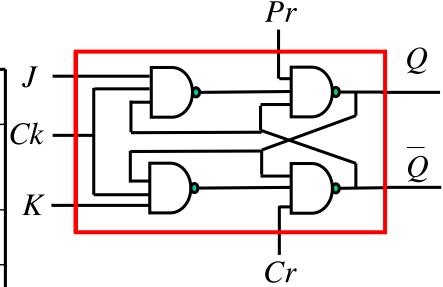

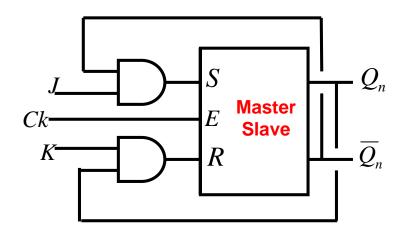

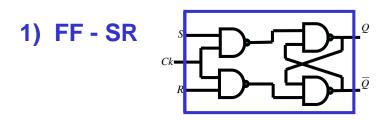

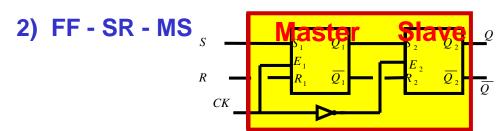

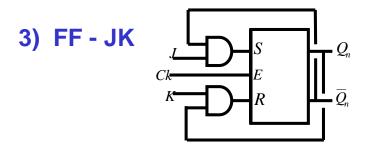

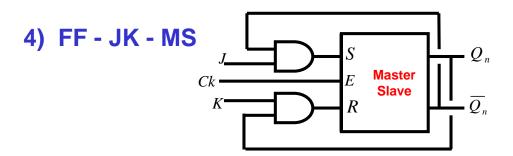

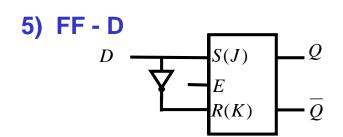

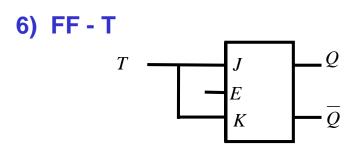

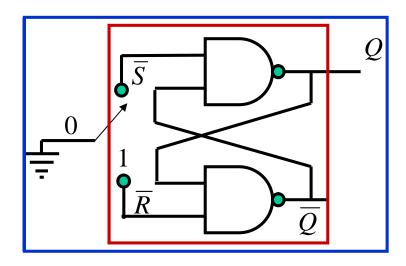

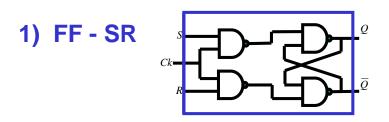

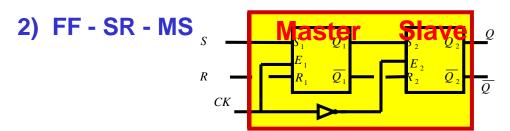

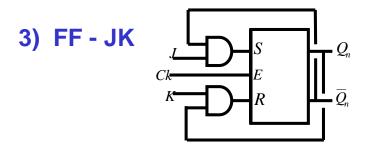

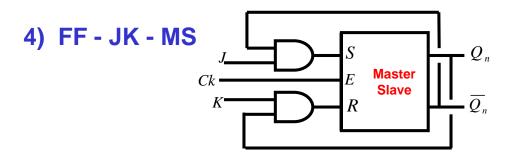

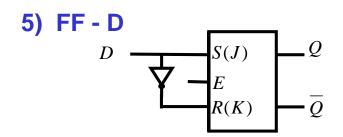

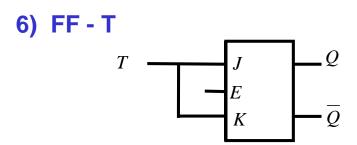

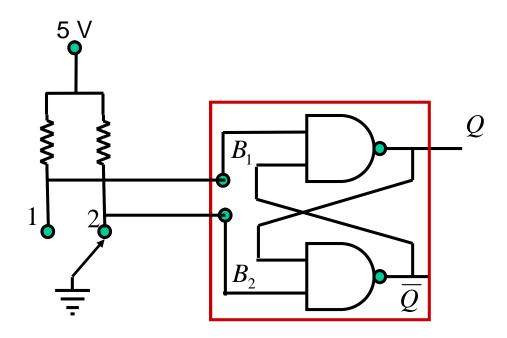

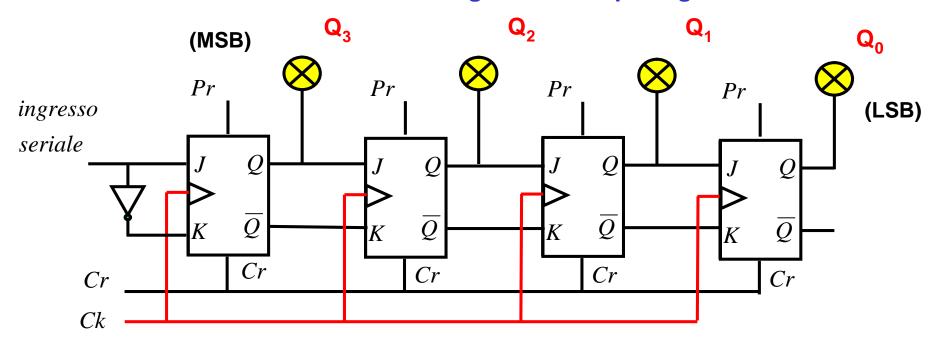

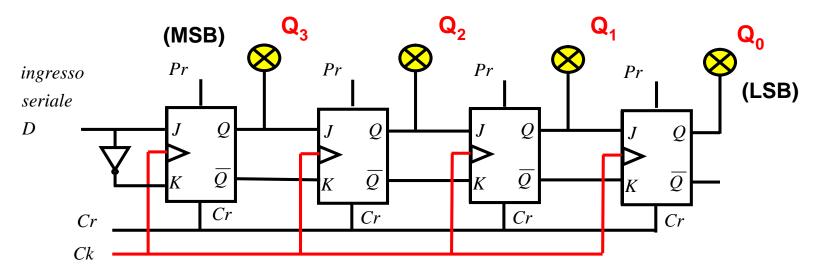

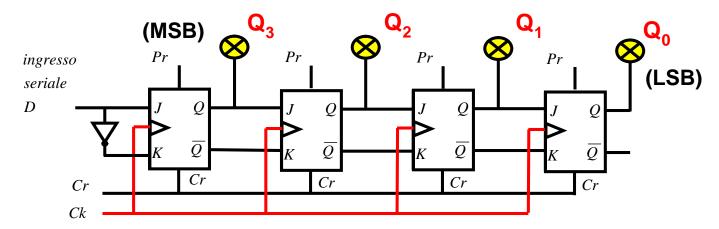

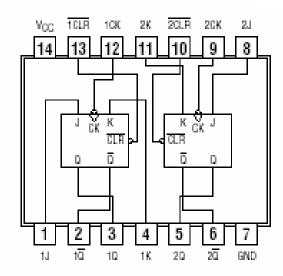

- ➤ Celle di memoria, FLIP-FLOP S-R, FLIP-FLOP J-K, FLIP-FLOP J-K Master-Slavel, FLIP-FLOP Delay, FLIP-FLOP Toggle

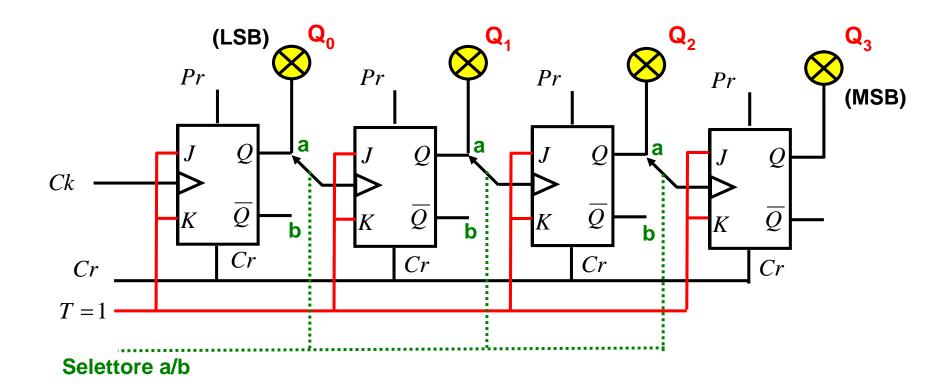

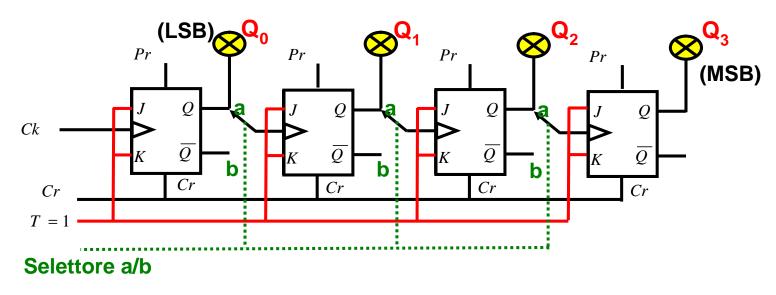

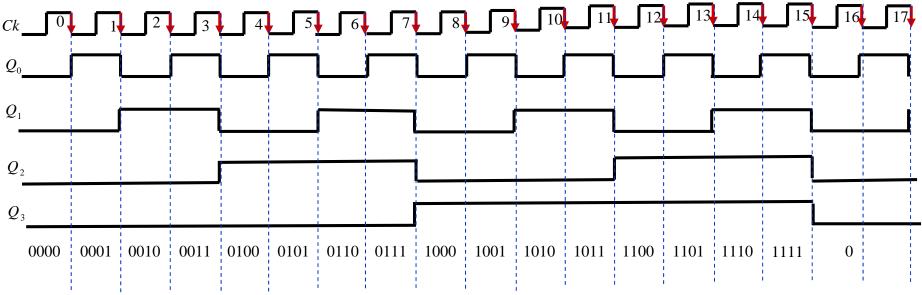

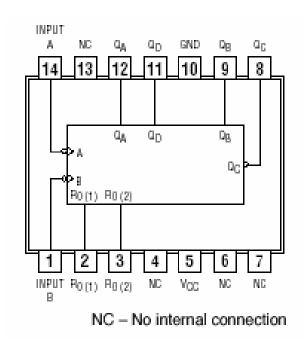

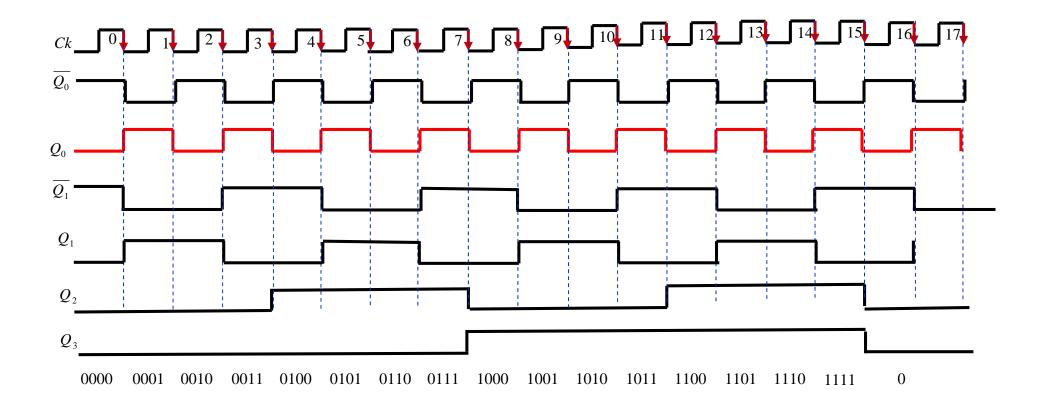

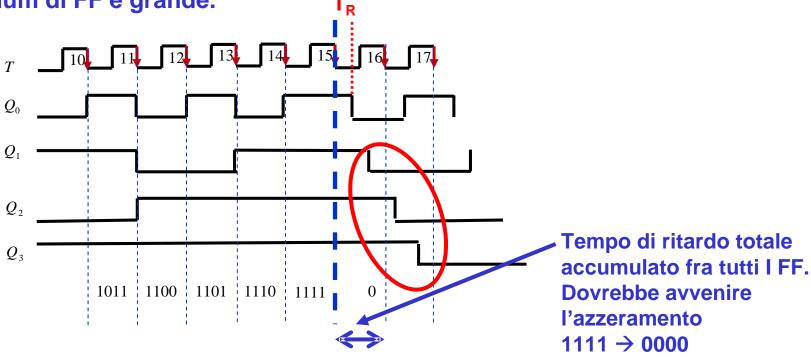

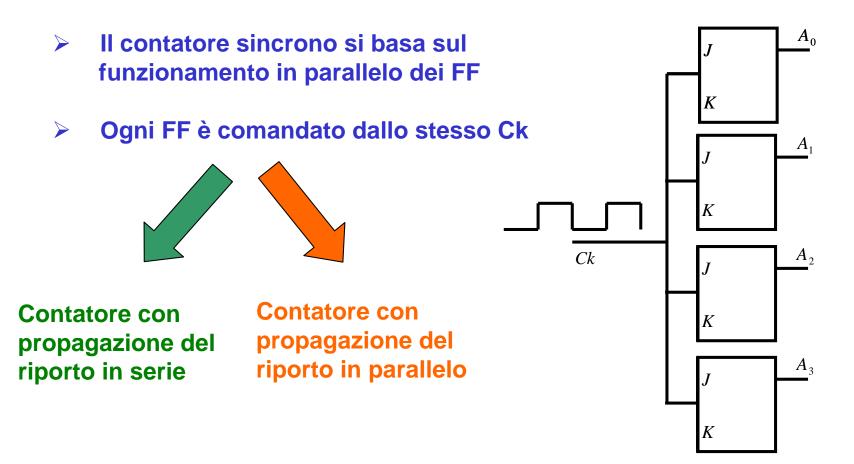

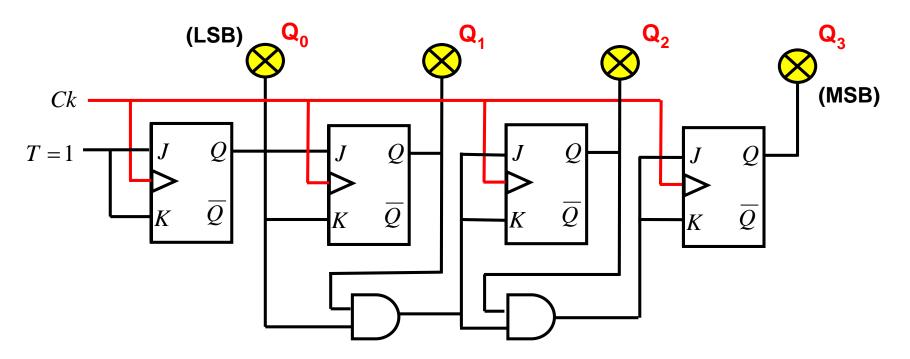

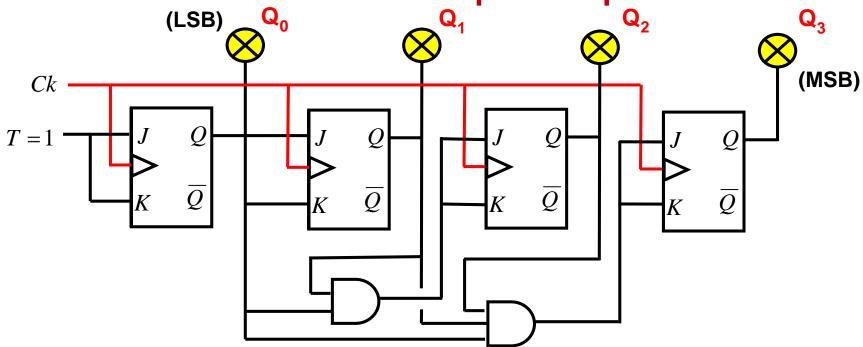

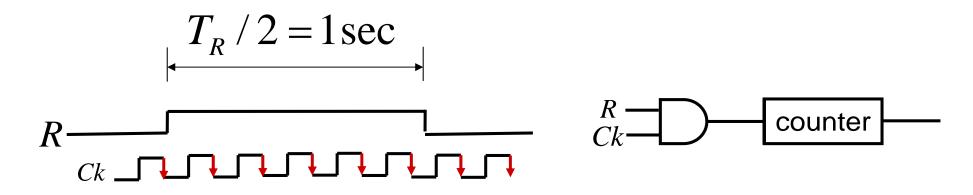

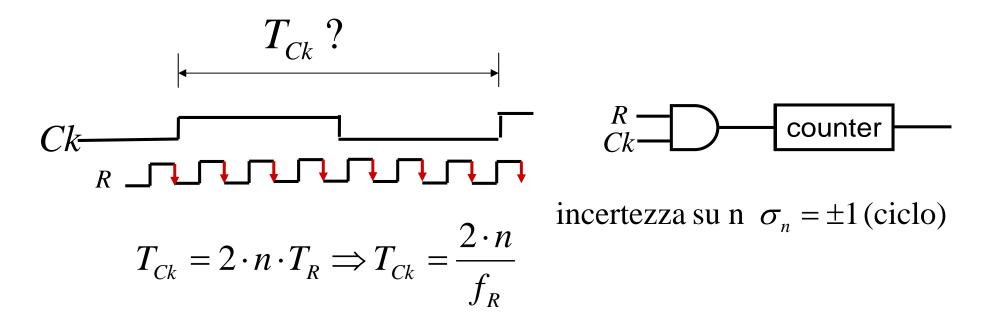

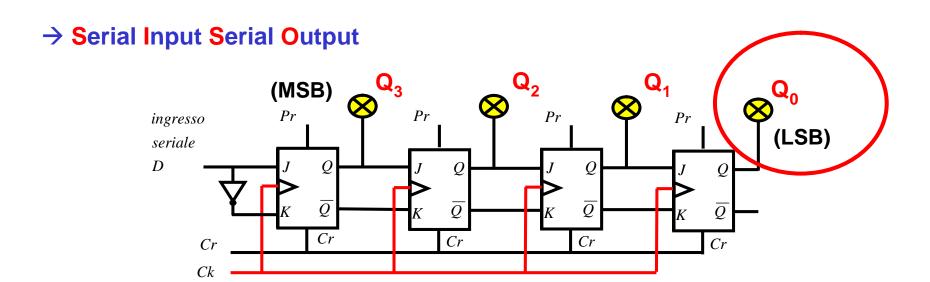

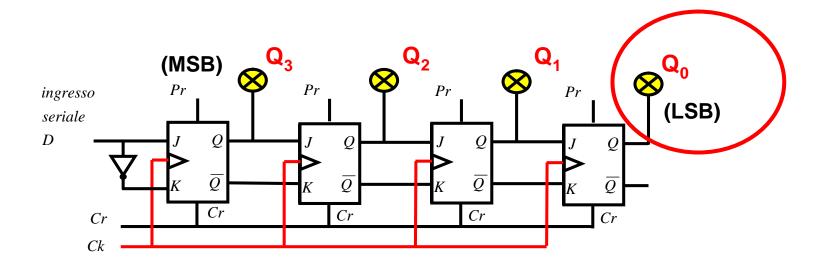

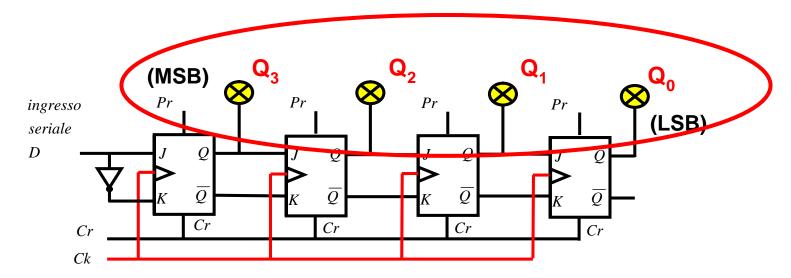

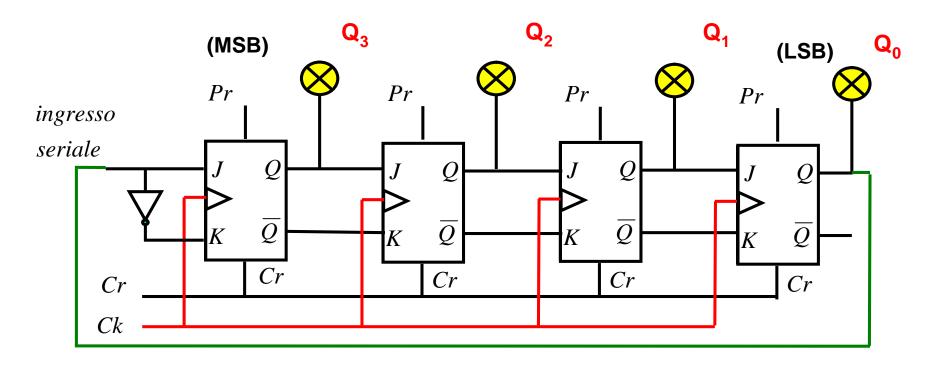

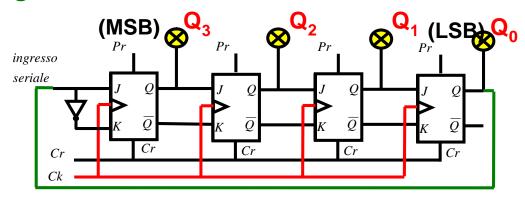

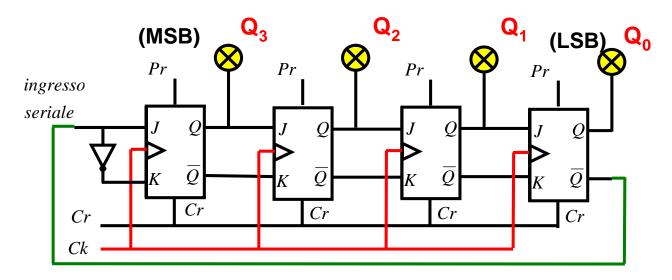

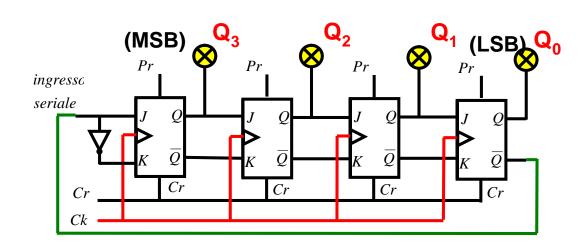

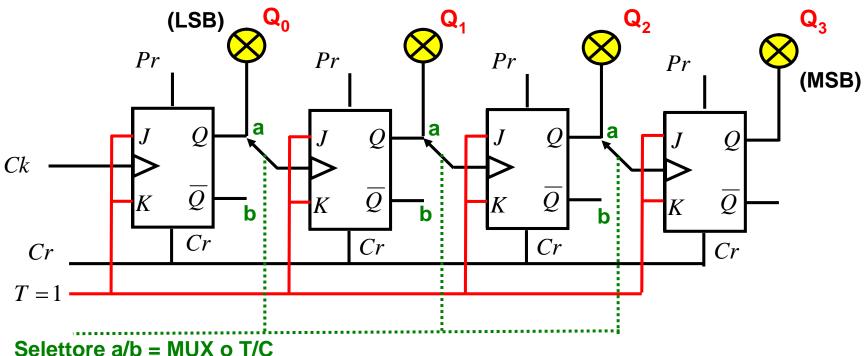

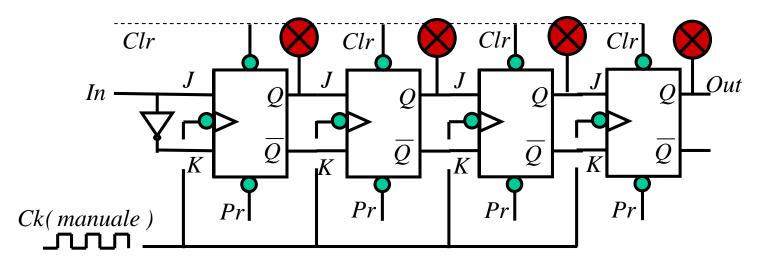

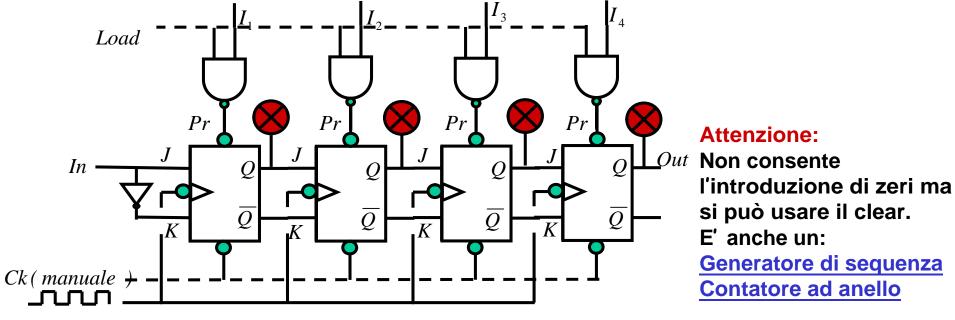

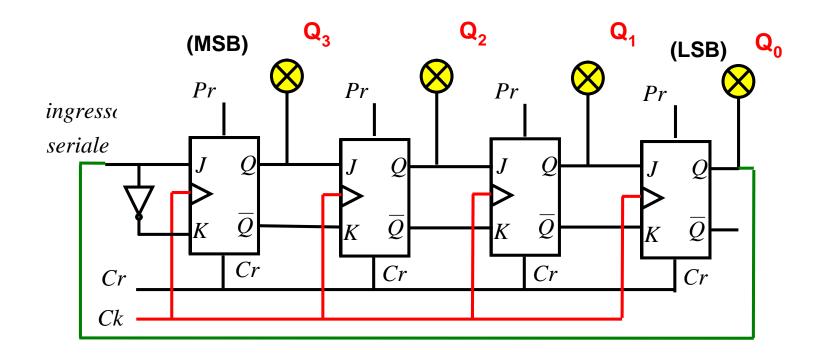

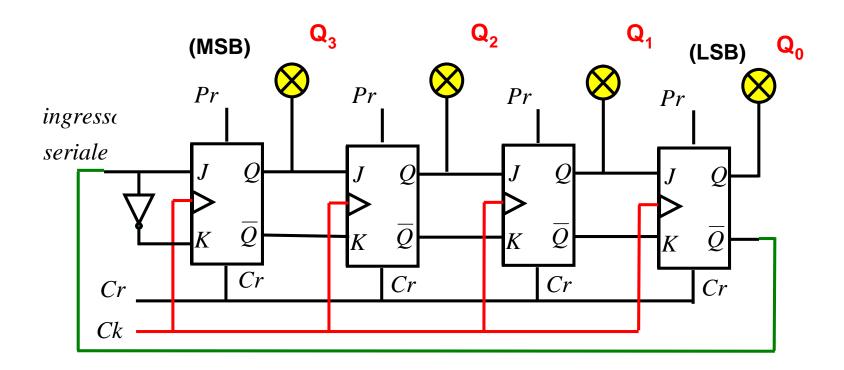

- ➤ Contatori asincroni, contatori sincroni, rigistri a scorrimento (Shift Register)

- Funzionamento SISO, SIPO, PIPO, PISO

#### 4. Applicazioni di elettronica digitale

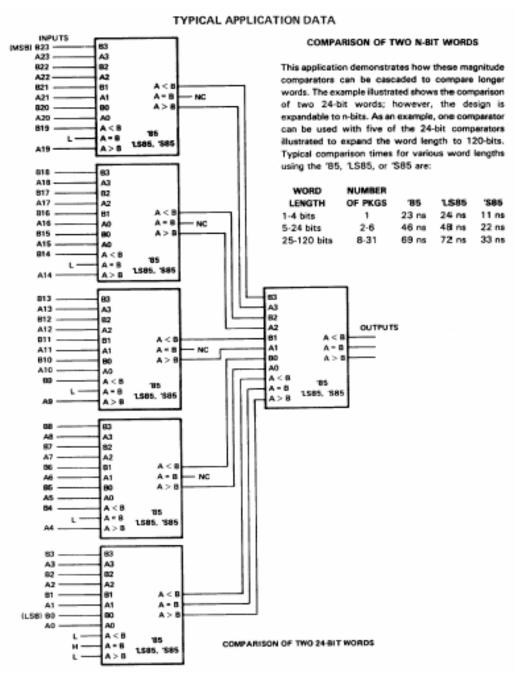

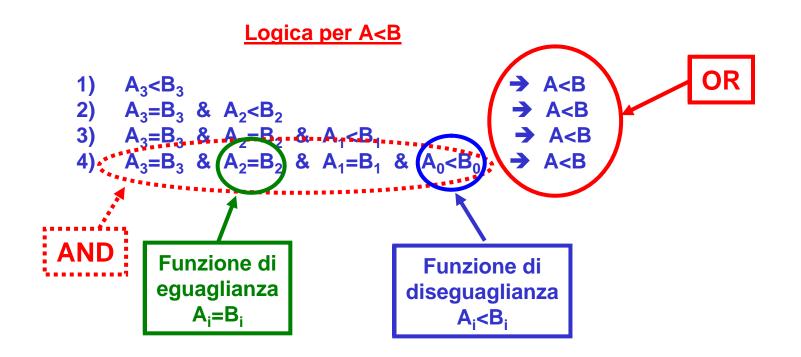

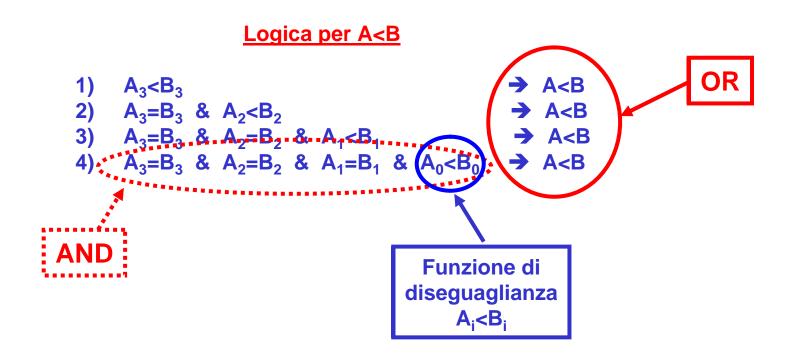

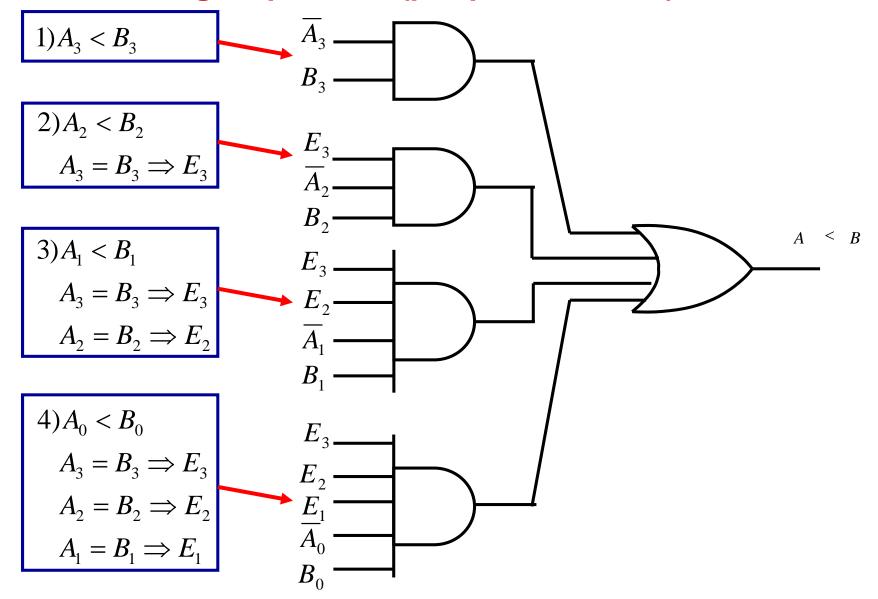

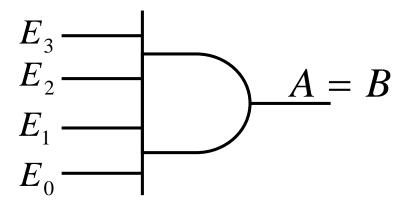

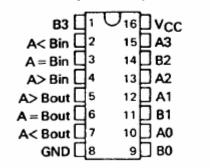

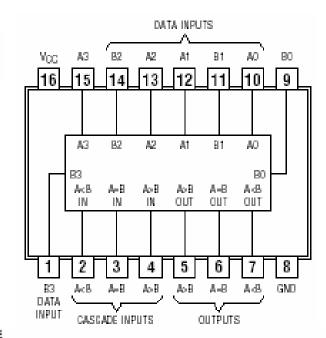

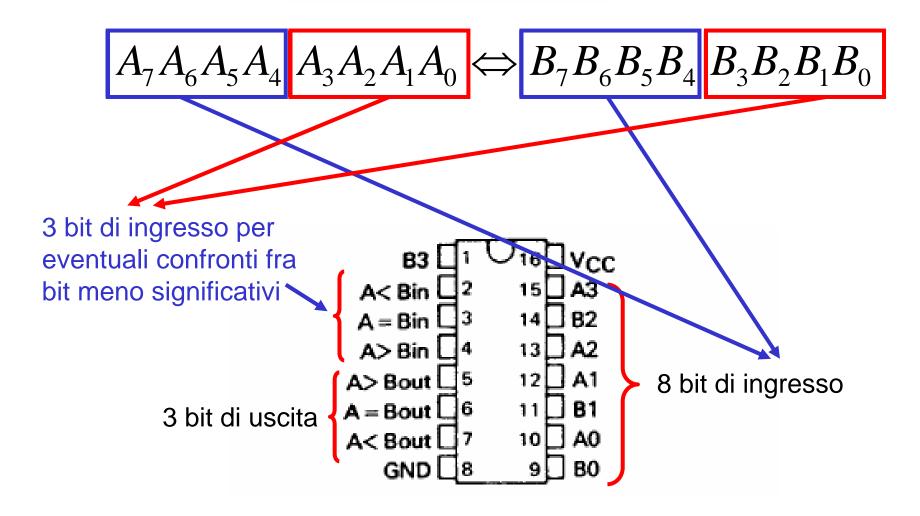

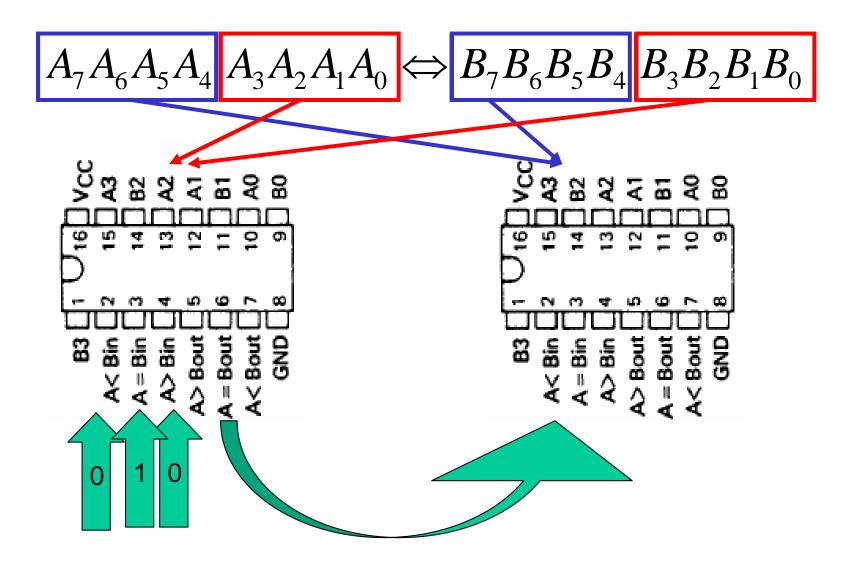

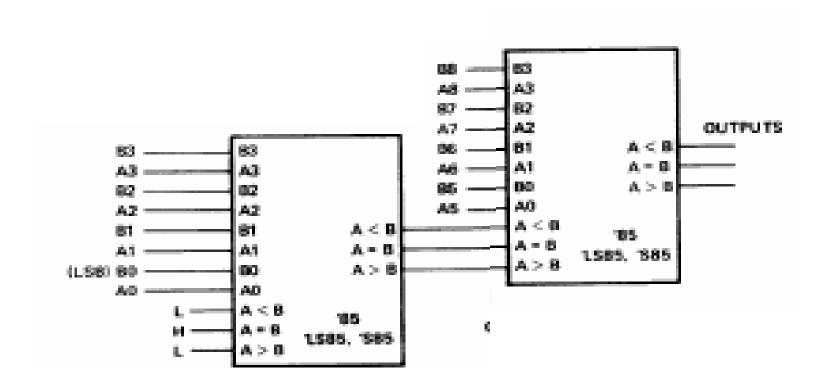

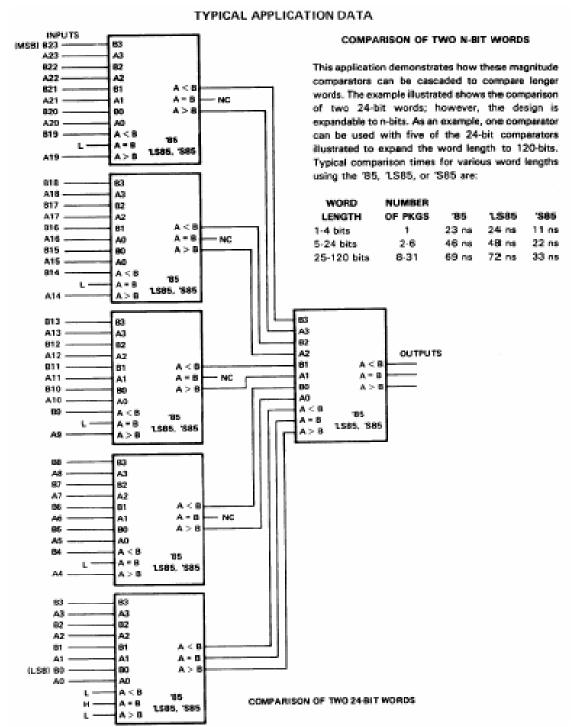

- ➤ Comparatori a più bit

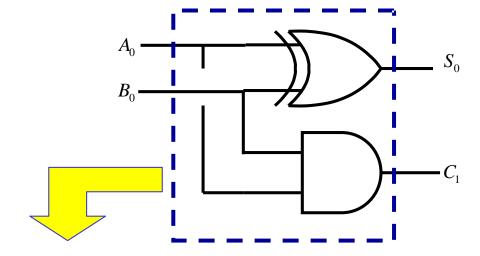

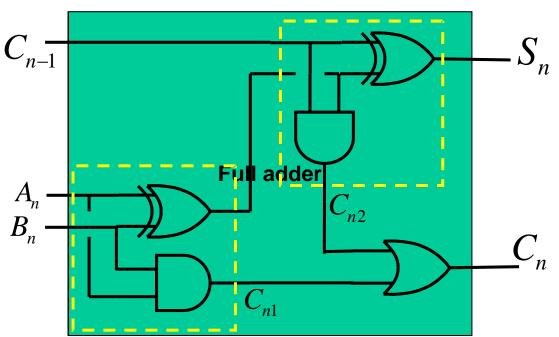

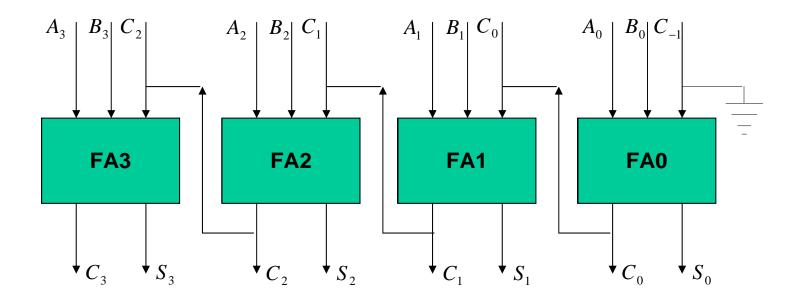

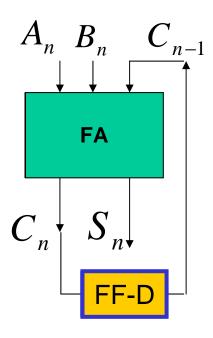

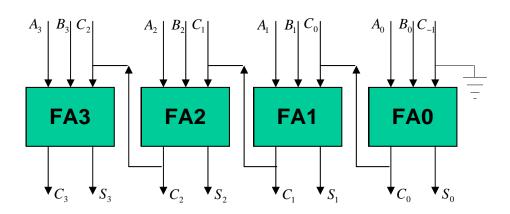

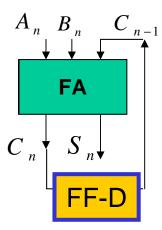

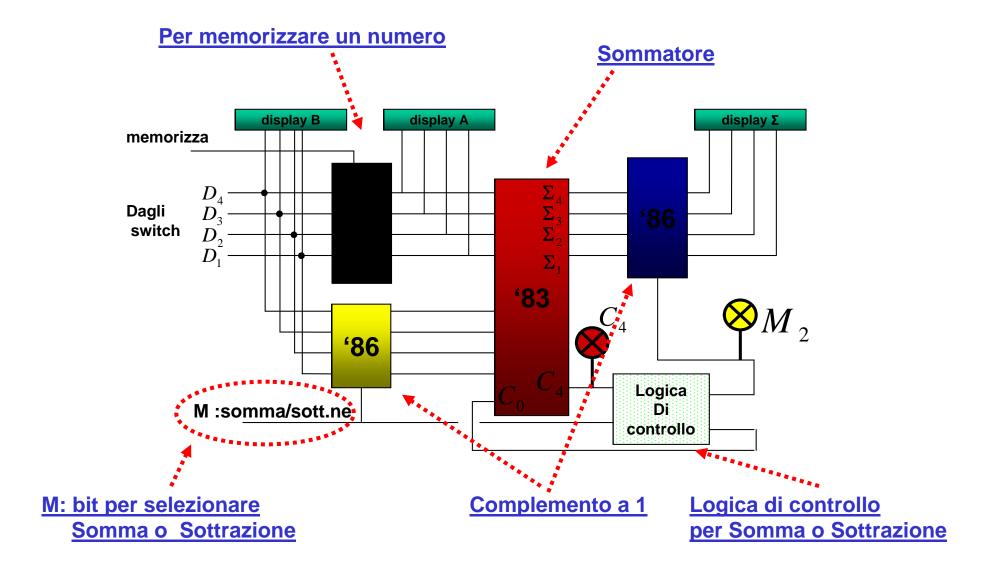

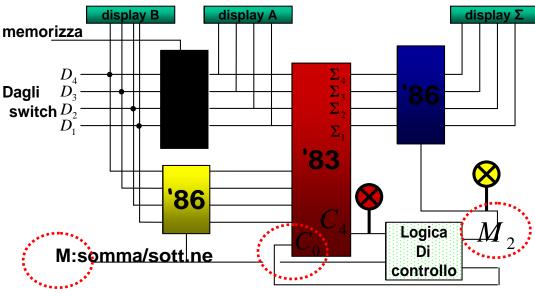

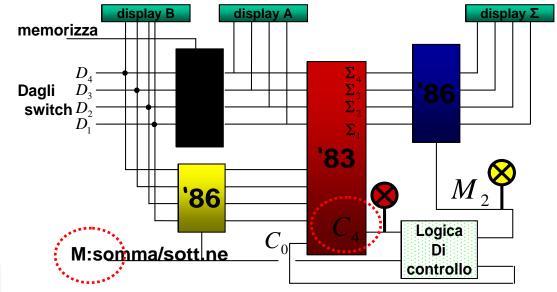

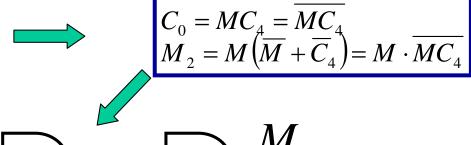

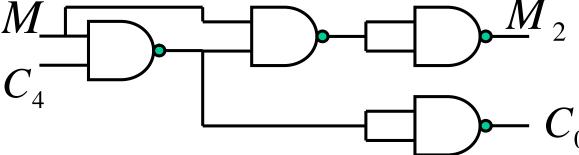

- > Sommatori e sottrattori

#### 5. Tipi di circuiti integrati e applicazioni

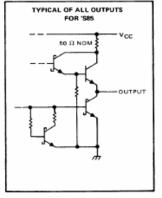

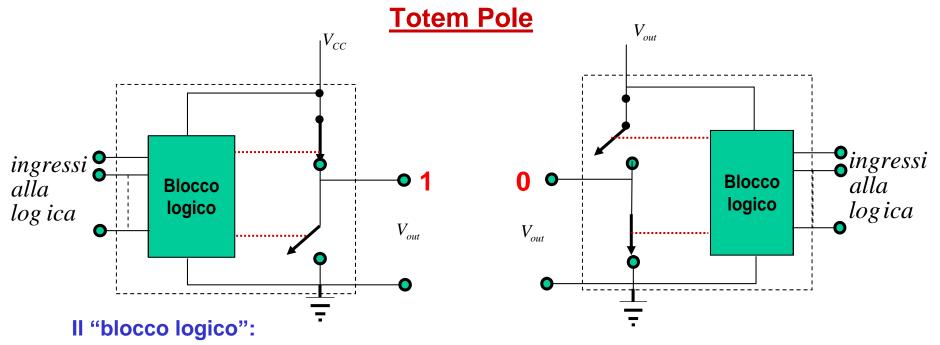

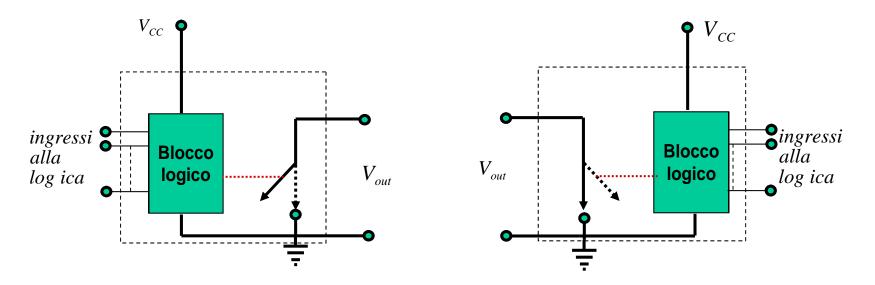

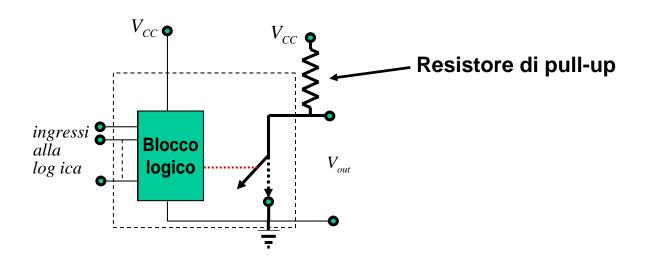

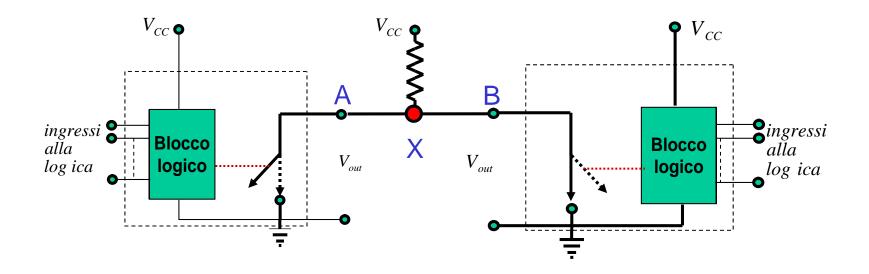

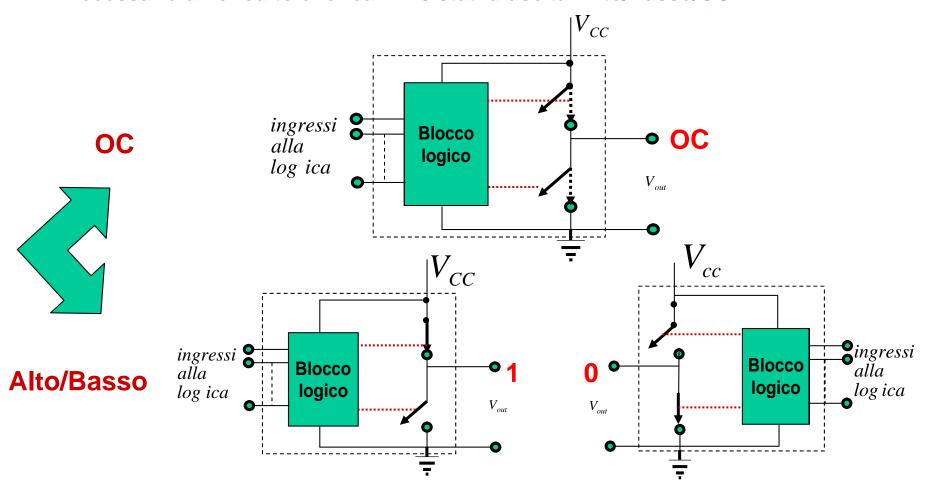

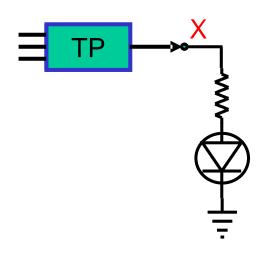

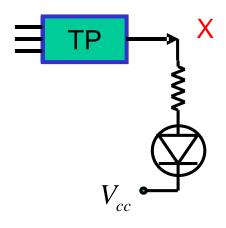

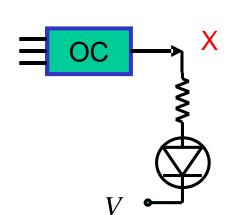

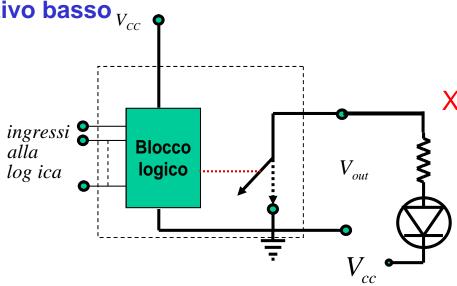

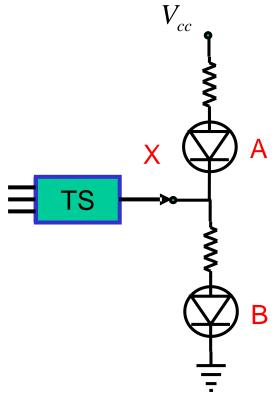

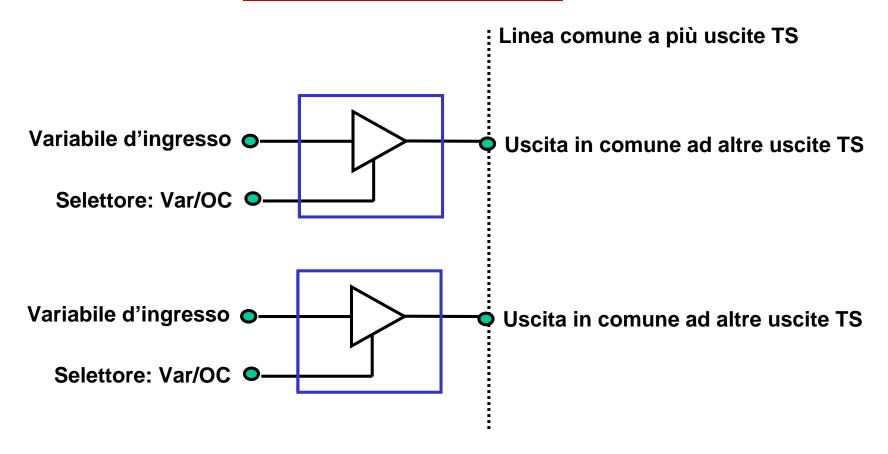

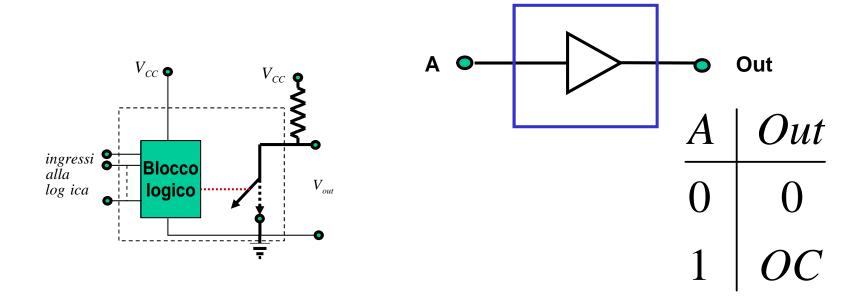

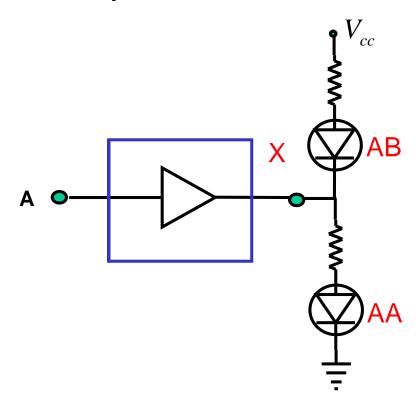

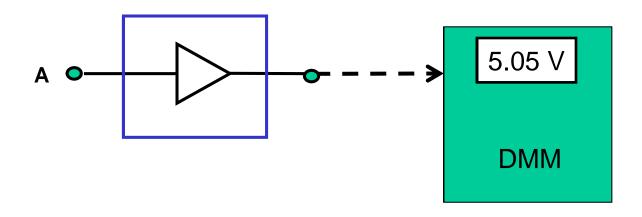

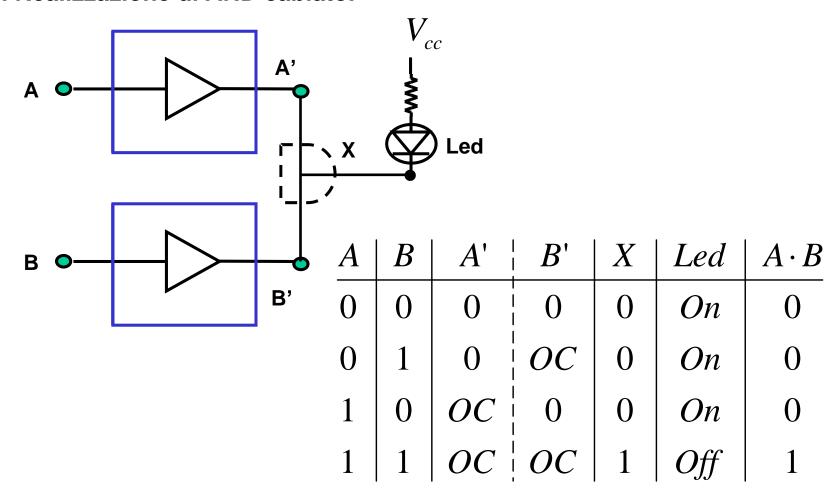

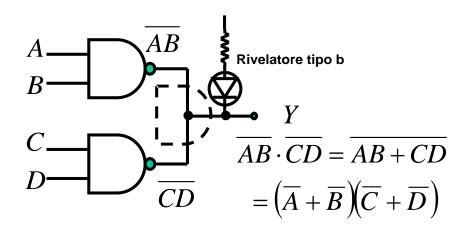

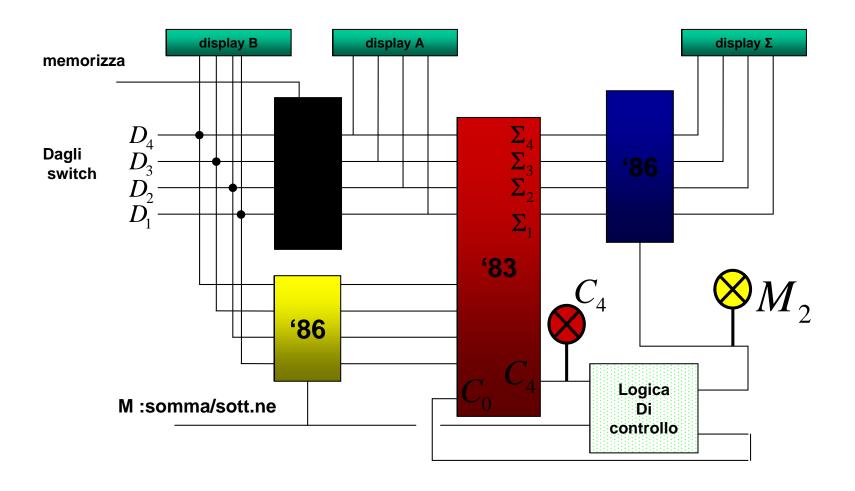

- ➤ I transitor: circuiti digitali con uscite Totem-Pole, Open-Collector, Three-State

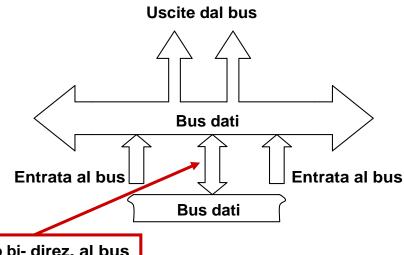

- ➤ Bus dati per la comunicazione di dati fra sistemi diversi

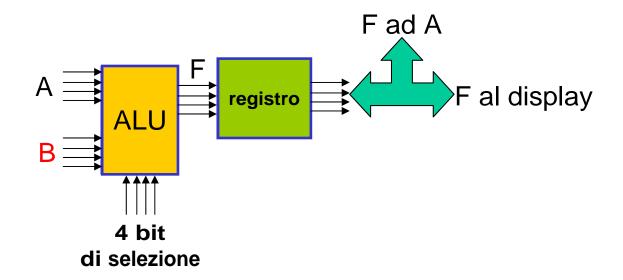

- Studio dell'unità aritmetico-logica (ALU)

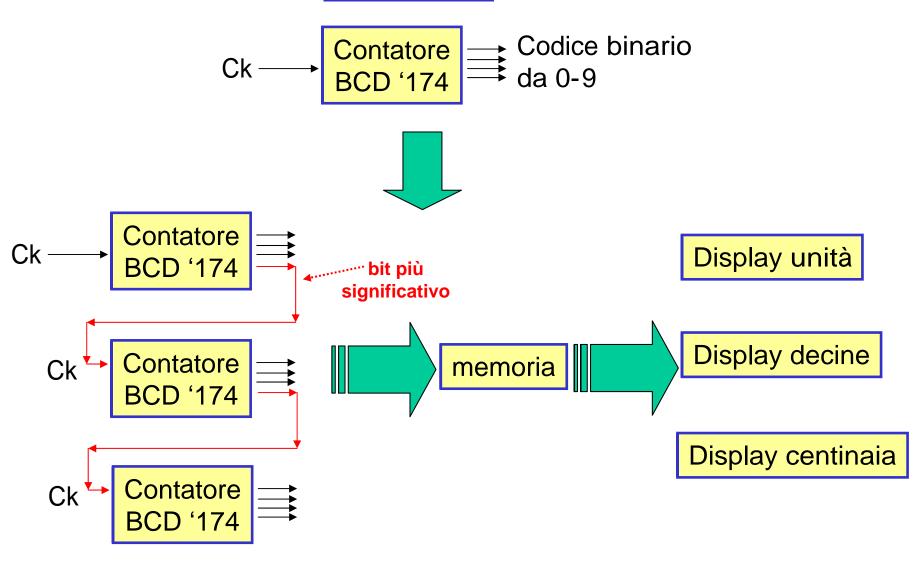

- Contatori di impulsi a 3 cifre

#### Cenni di Elettronica Analogica

#### 1. Strumenti matematici e fisici per l'elettronica analogica

- > Funzioni periodiche

- ➤ Sviluppo in serie di Fourier

- ➤ Alcune forme d'onda particolari

- Grandezze fondamentali dell'elettronica analogica

#### 2. Dispositivi elettrici fondamentali e risoluzioni delle reti elettriche

- > Resistenze, condensaori, induttanze

- Leggi e teoremi per l'elettronica analogica

- > Funzionamento delle reti elettriche in regime sinusoidale

#### 3. Trattazione di particolari applicazioni di interesse pratico

- > Partitore di tensione

- ➤ Convertitore Digitale-Analogico

- Circuiti R-C e C-R e loro utilizzo come filtri

- Partitori capacitivi e compensati

#### Esperienze di Laboratorio Parte I

#### Programma del corso

- ➤ D-1

- o Operazione con le porte logiche elementari

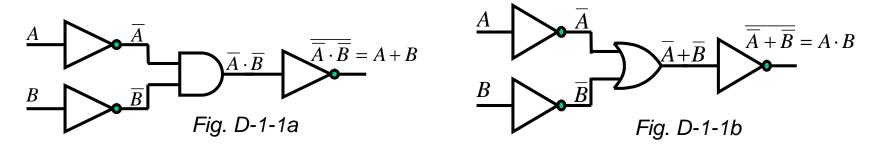

- o Verifica del teorema di De Morgan

- o Flusso di segnali digitali (gate)

- ➤ D-2

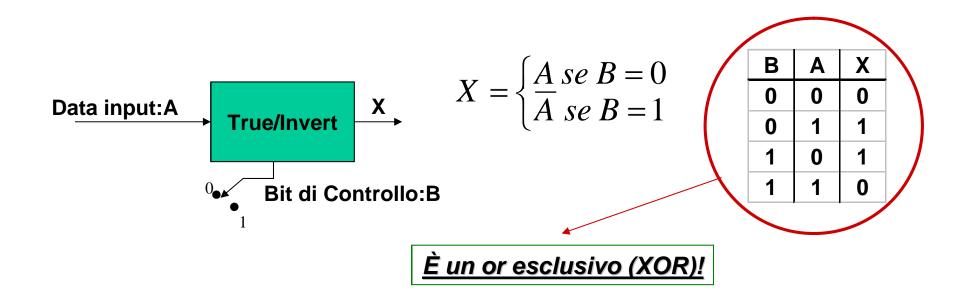

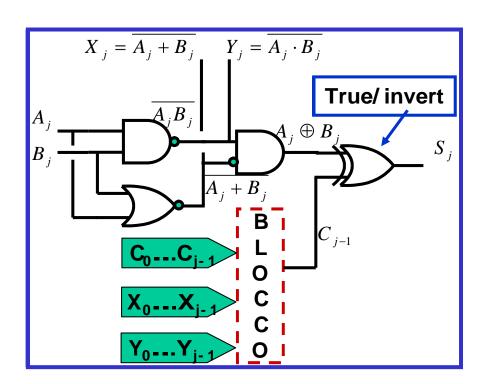

- o Realizzazione di un True/Invert

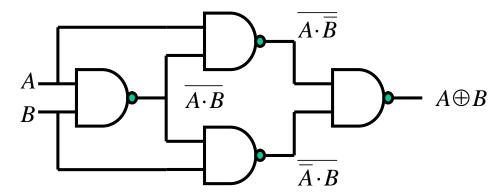

- o Realizzazione di EXOR (EXNOR) con sole porte NAND (NOR)

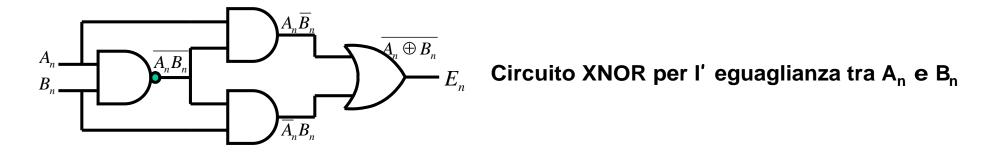

- o Funzione di uguaglianza

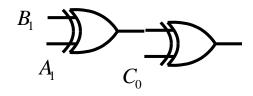

- o Comparatore digitale a un bit

- ➤ D-3

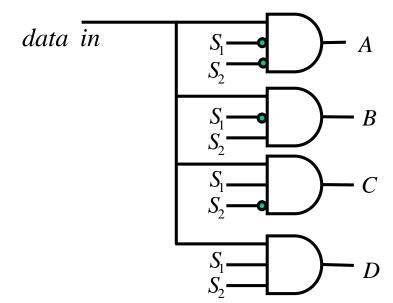

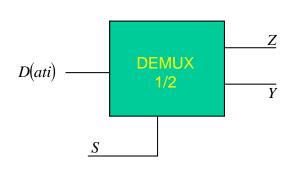

- o MUX (Multiplexer)

- o DeMUX (DeMultiplexer)

# ?

#### Esperienze di Laboratorio Parte II

- ➤ D-4

- o Operazioni con i FLIP-FLOP SR

- o Operazioni con FLIP-FLOP con ENABLE

- o Master-Slave non trasparente

- o Master-Slave Toggle

- > D-5

- o Operazioni con FLIP-FLOP JK

- o Realizzazione di un contatore binario

- o Realizzazione di un registro a scorrimento

- o Funzioni SISO, SIPO, PIPO, PISO

#### Esperienze di Laboratorio Parte III

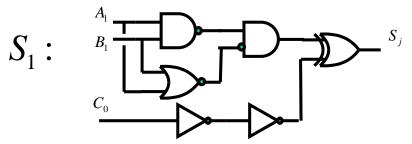

- > D-6

- o Realizzazione di un comparatore a più bit

- o Realizzazione di un sommatore

#### Esperienze di Laboratorio Parte IV

- > D-7

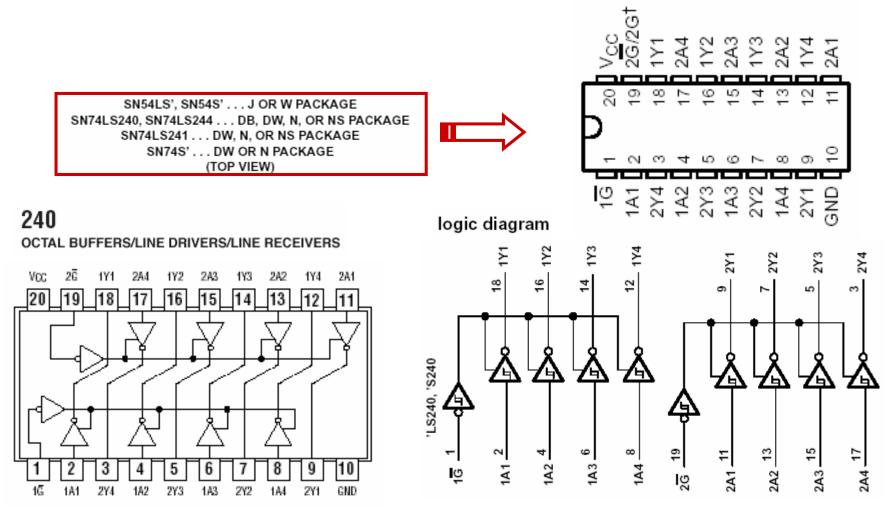

- o Utilizzo dei dispositivi Totem-Pole, Open-Collector e Tristate

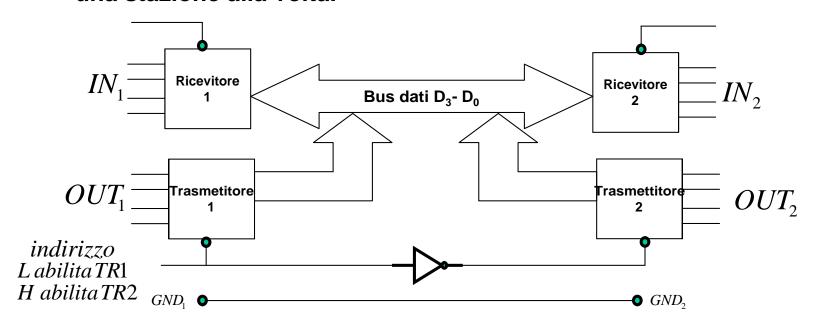

- Comunicazione tramite bus tristate

- ➤ D-8

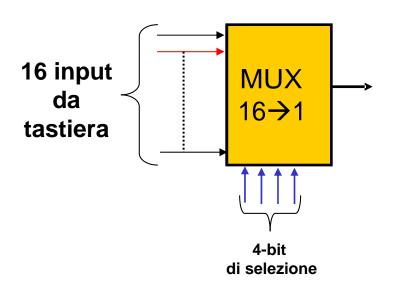

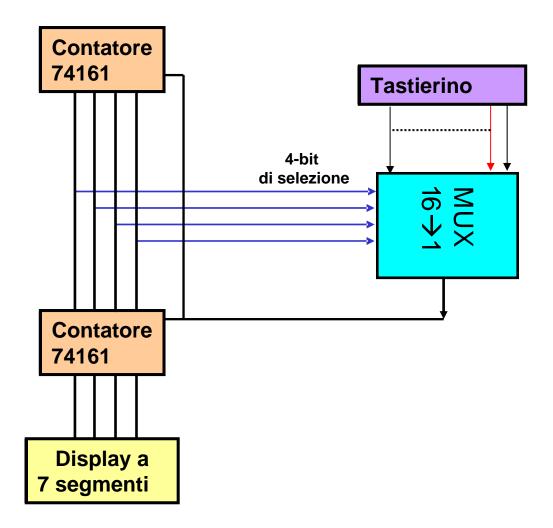

- Trasmissione dati da tastiera

- > D-9

- o Utilizzo dell'unità aritmetico-logica (ALU)

- > D-10

- o Realizzazione di un contatore di impulsi a 3 cifre.

## Laboratorio di Elettronica Elettronica Digitale

#### Parte I

Corso di Laurea in TFI Anno Accademico 2007-2008

#### •ELETTRONICA

perché ci interessa?

#### SISTEMI TIPICI

sistema informatico impianti HIFI

#### **SEGNALI**

analogici digitali

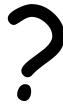

#### •APPROCCIO SISTEMISTICO

sistemi

→→ sistema per la misura della velocità del suono

apparati

**→→** Oscilloscopio

blocchi funzionali

→→ amplificatore, trigger di Schmidt, alimentatori...

schemi circuitali

→→ molto complessi

componenti

→→ molto pochi e ricorrenti:

circ. integrati e componenti

Riduce tutto, a qualunque livello, al concetto di blocco funzionale:

radio, TV, stereo, strumentazione varia.....

A.A. 2008-09 1° trimestre Dott. M. Andreotti

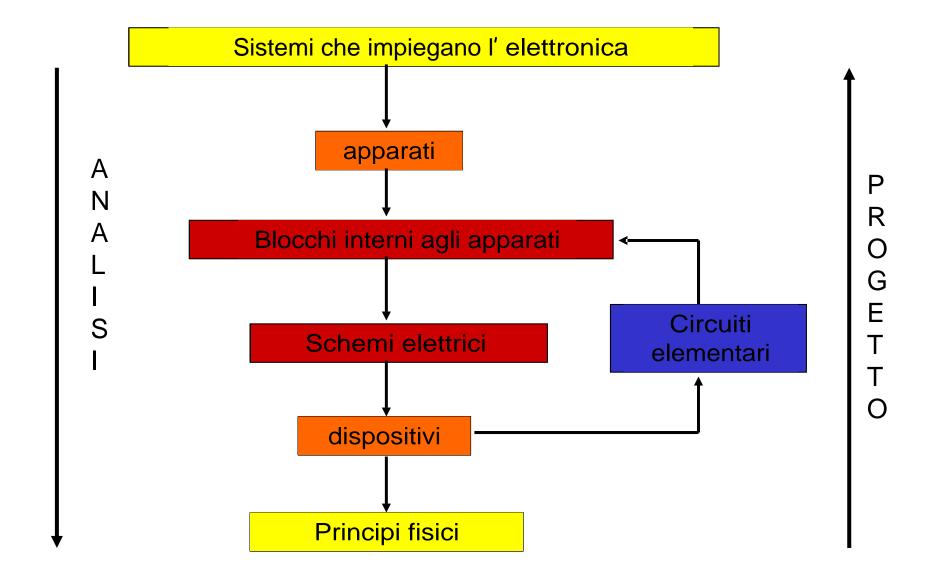

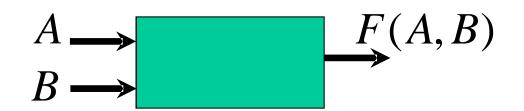

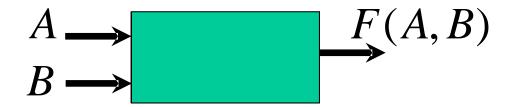

#### IL BLOCCO FUNZIONALE

#### Proprietà generali dei blocchi:

È completamente determinato dalla funzione che lega le variabili di ingresso e di uscita

#### Possono essere:

Digitali : elettronica digitale

Analogici : elettronica analogica

Di conversione : A/D & D/A

#### Possono anche essere:

Lineari e non lineari

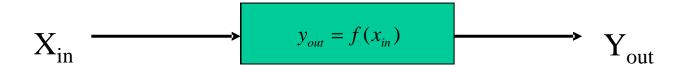

#### **ESEMPI**

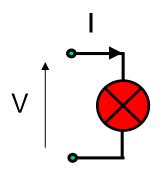

#### Segnali Digitali/Analogici

Segnale |

Segnale elettrico caratterizzato da certe grandezze:

- Tensione V (V) (differenza di potenziale elettrico)

- corrente I (A) (movimento di elettroni)

- tempo (s)

#### Segnali <u>Digitali</u>/Analogici

- ✓ Valori della tensione in funzione del tempo:

- ☐ tensione continua di una pila (in funzione del tempo è una retta)

- ☐ tensione alternata della rete domestica (sinusoide)

- ✓ segnale analogico: può assumere tutti i valori di tensione

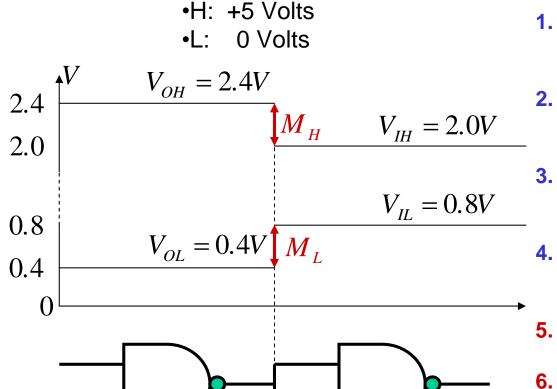

- ✓ <u>segnale digitale: può assumere solo due valori di tensione</u>

- > i 2 valori dipendono dalla famiglia di segnali che si usano

- > e dalla logica

• due livelli di tensione:  $V_{HIGH}$  (H)/  $V_{LOW}$  (L)

#### •famiglie logiche:

TTL, HTL,ECL, MOS,CMOS....

• logica

positiva:  $H \rightarrow T/1$ ,  $L \rightarrow F/0$

negativa: L  $\rightarrow$ T/1, H  $\rightarrow$ F/0

•funzioni logiche

le stesse per tutte

| Family                       | Basic<br>gate | Fanout | Pd<br>(mW/gate) | Noise<br>immunity | Prop. delay<br>(ns/gate) | Clock<br>(MHz) |

|------------------------------|---------------|--------|-----------------|-------------------|--------------------------|----------------|

| ${ m TTL}$                   | NAND          | 10     | 10              | VG                | 10                       | 35             |

| TTL-H                        | NAND          | 10     | 22              | VG                | 6                        | 50             |

| TTL-L                        | NAND          | 20     | 1               | VG                | 33                       | 3              |

| TTL-LS                       | NAND          | 20     | 2               | VG                | 9.5                      | 45             |

| TTL-S                        | NAND          | 10     | 19              | VG                | 3                        | 125            |

| TTL-AS                       | NAND          | 40     | 10              | VG                | 1.5                      | 175            |

| TTL-ALS                      | NAND          | 20     | 1               | VG                | 4                        | 50             |

| ECL 10K                      | OR-NOR        | 25     | 40-55           | P                 | 2                        | >60            |

| ECL100K                      |               |        | 40-55           | P                 | 0.75                     | 600            |

| MOS                          | NAND          | 20     | 0.2-10          | G                 | 300                      | 2              |

| 74C                          | NOR/NAND      | 50     | 0.01/1          | VG                | 70                       | 10             |

| 74HC                         | NOR/NAND      | 20     | 0.0025/0.6      | VG                | 18                       | 60             |

| 74HCT                        | NOR/NAND      | 20     | 0.0025/0.6      | VG                | 18                       | 60             |

| 74AC                         | NOR/NAND      | 50     | 0.005/0.75      | VG                | 5.25                     | 100            |

| 74ACT                        | NOR/NAND      | 50     | 0.005/0.75      | VG                | 4.75                     | 100            |

| A.A. 2008-09<br>1° trimestre |               |        | Dott. M. And    |                   | 19                       |                |

#### PERCHE' APPROCCIO SISTEMISTICO?

- sistema = blocco

- blocco di natura elettronica

#### PERCHE' PRIMA L' ELETTRONICA DIGITALE?

- più facile

- non richiede nozioni preliminari

- candidato ideale al tipo di approccio

- due soli stati (variaili di ingresso: tensioni)

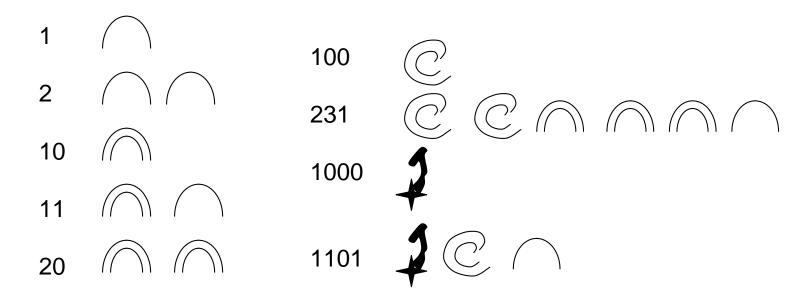

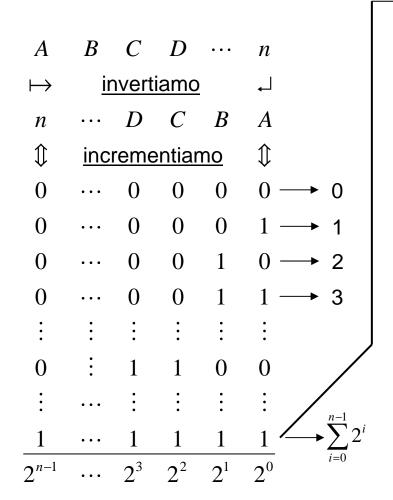

#### Sistemi di Numerazione

- Numero

- concetto non primitivo

- serve per "quantificare" la realtà

- Sistema di numerazione:

- insieme finito di simboli

- simboli organizzati in sequenze secondo "regole"

Il sistema più antico è (forse) quello egizio ed ha circa 5000 anni. E' di tipo decimale con simboli ripetuti per i multipli di una stessa quantità.

• I Sumeri avevano l' unità numerica fondamentale che corrisponde al nostro 60

nostro sistema di misura degli angoli?

#### Non hanno lo zero ed i simboli sono posizionali

lo zero introdotto forse nella civiltà indiana e poi arriva in Europa portato dagli Arabi

22

- I simboli da noi usati oggi (indo-Arabi) risalgono al X secolo

- I numeri frazionari arrivano solo nel XVI secolo

- Il punto decimale viene introdotto verso la metà del XVII secolo

#### I sistemi di numerazioni usati sono caratterizzati da:

Posizionale: sistema in cui il valore associato ad ogni simbolo dipende dalla sua posizione nella "stringa"

Basi: numero di simboli usati nella numerazione

Peso: il fattore per cui il simbolo (numero) deve esse moltiplicato per potere essere confrontato con gli altri simboli (numeri): potenza ad esponente variabile della base del sistema di numerazione

#### Vediamo alcuni esempi →

#### Sistema decimale:

- è in base 10

- 10 simboli: 0-9

- è posizionale

**Esempio:** 4518,23

4 5 1 8, 2 3 10<sup>3</sup> 10<sup>2</sup> 10<sup>1</sup> 10<sup>0</sup>, 10<sup>-1</sup> 10<sup>-2</sup>

Che significa:

4000+500+10+8+0,2+0,03

#### Sistema binario:

- è in base 2

- 2 simboli: 0,1

- è posizionale

**Esempio: 1001,01**

1 0 0 1, 0 1 2<sup>3</sup> 2<sup>2</sup> 2<sup>1</sup> 2<sup>0</sup>, 2<sup>-1</sup> 2<sup>-2</sup>

Che significa:

8+0+0+1+0+0.25

In generale in base "R":

$$N = C_{n-1} \cdot R^{n-1} + C_{n-2} \cdot R^{n-2} + \dots + C_0 \cdot R^0 + C_{-1} \cdot R^{-1} + \dots$$

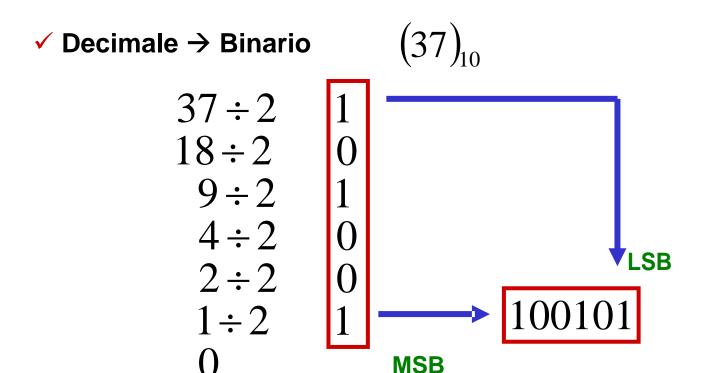

#### Come si passa da un sistema all' altro?

✓ Binario → Decimale

$$(1100101)_2 =$$

$$1 \cdot 2^6 + 1 \cdot 2^5 + 0 \cdot 2^4 + 0 \cdot 2^3 + 1 \cdot 2^2 + 0 \cdot 2^1 + 1 \cdot 2^0 = (101)_{10}$$

#### Sistema ottale:

- è in base 8

- 8 simboli: 0-7

- è posizionale

**Esempio:** (514,23)<sub>8</sub>

5 1 4, 2 3 8<sup>2</sup> 8<sup>1</sup> 8<sup>0</sup>, 8<sup>-1</sup> 8<sup>-2</sup>

Esempio: (456)<sub>8</sub>

110011101110

#### Sistema esadecimale:

- è in base 16

- 16 simboli: 0-9,A,B,C,D,E,F

- è posizionale

Esempio: (3AFF9)<sub>16</sub>

3 10 15 15 9 16<sup>4</sup> 16<sup>3</sup> 16<sup>2</sup> 16<sup>1</sup> 16<sup>0</sup>

Esempio:(B7F)<sub>16</sub>

1011101111111

#### Il sistema binario

- è in base 2

- 2 simboli: 0,1

- è posizionale

### Regole pratiche:

Somma

$$0 + 0 = 0$$

$0 + 1 = 1$

$1 + 1 = 10$  (0 con riporto di 1)

Sottrazione  $0 - 0 = 0$

$1 - 0 = 1$

$1 - 1 = 0$

$0 - 1 = 1$  con richiamo di 1

#### Alcuni esempi:

la sottrazione è complicata

#### → introduciamo la COMPLEMENTAZIONE

#### **Complementazione**

- Decimale -- a 9 dato xxx il suo complemento a 9 è 999-xxx -- a 10 dato xxx il suo complemento a 10 è 1000-xxx (complemento a 9 + 1)

- Binario -- a 1 dato xxx il suo complemento a 1 è 111-xxx -- a 2 dato xxx il suo complemento a 2 è 1000-xxx (complemento a 1 + 1)

→ anzichè eseguire una sottrazione utilizziamo un'alternativa:

- Decimale

- 1) eseguiamo il complemento a 10 del minuendo

- 2) se sottraendo > minuendo: a) sommiamo al sottraendo 1)

- b) scartiamo l'eventuale riporto

- se sottraendo < minuendo: a) sommiamo al sottraendo 1)

- b) eseguiamo il complemento a 10 del risultato

- c) ne cambiamo il segno

- Binario

- 1) eseguiamo il complemento a 2 del minuendo

- 2) se sottraendo > minuendo: a) sommiamo al sottraendo 1)

- b) scartiamo l'eventuale riporto

- se sottraendo < minuendo: a) sommiamo al sottraendo 1)

- b) eseguiamo il complemento a 2 del risultato

- c) ne cambiamo il segno

#### - Esempio Decimale sottrendo > minuendo 457 -457 + $129 = \rightarrow \text{compl}(10) \rightarrow 871 =$ sottraendo < minuendo 129 +129 - $547 = \rightarrow \text{compl}(10) \rightarrow 453 =$ 582 compl(10)← $418 \rightarrow CHS \rightarrow -418$

- Esempio binario

sottrendo > minuendo

$$1100 - 1100 + 1100 + 1101 = 1001 = 1001$$

sottraendo < minuendo

$101 - 101 + 11011 = 10101 = 101010$

$10110 \rightarrow CHS \rightarrow -10110$

#### - Esempio Decimale

$$457 - \underbrace{129 =} \rightarrow \text{compl}(10) \rightarrow \underbrace{871 =} = xxx - 1000 + 1000 - yyy = \\ = xxx - 1000 + yyy_{10} = \\ = [xxx + yyy_{10}] - 1000$$

xxx - yyy =

#### sottraendo < minuendo

$$129 - 129 + 547 = \rightarrow \text{compl}(10) \rightarrow 453 = 582$$

$$\text{compl}(10) \rightarrow 418 \rightarrow \text{CHS} \rightarrow -418$$

- L'esempio binario è del tutto analogo a quello decimale

- -Perchè tutta questa confusione con complementi a 1 o a 2 e poi cambi di segno etc etc?

- → è un modo per avere sempre operazioni con risultati positivi

- → situazione meglio gestibile nella realizzazione pratica di circuiti elettronici per la realizzazione delle operazioni.

- → ne studieremo i dettagli più avanti

Un primo progetto per l'esame finale

#### Significato matematico della complementazione in generale (decimale)

$$xxx - yyy =$$

$$= xxx - 1000 + 1000 - yyy =$$

$$= xxx - 1000 + yyy_{10} =$$

$$= [xxx + yyy_{10}] - 1000$$

$$xxx - yyy =$$

$$= xxx - 999 + 999 - yyy =$$

$$= xxx - 999 + yyy_9 =$$

$$= [xxx + yyy_9] - 999 =$$

$$= (-1) \cdot [xxx + yyy_9]_9 =$$

$$= (-1) \cdot [xxx + yyy_9]_{10} + 1 = \dots$$

$$xxxx - yy =$$

$$= xxxx - 10000 + 10000 - yy = xxx - 10000 + yy_{10}$$

$$= xxxx - 9999 + 9999 - yy = xxx - 9999 + yy_{9}$$

Per seguire le regole di prima Il complemento si effettua guardando al membro con maggior numero di cifre

#### Significato matematico della complementazione in generale (binario)

$$xxx - yyy =$$

=  $xxx - 1000 + 1000 - yyy =$

=  $xxx - 1000 + yyy_2 =$

=  $[xxx + yyy_2] - 1000$

$$xxx - yyy =$$

$$= xxx - 111 + 111 - yyy =$$

$$= xxx - 111 + yyy_1 =$$

$$= [xxx + yyy_1] - 111 =$$

$$= (-1) \cdot [xxx + yyy_1]_1 =$$

$$= (-1) \cdot [xxx + yyy_1]_2 + 1 = \dots$$

$$xxxx - yy =$$

$$= xxxx - 10000 + 10000 - yy = xxx - 10000 + yy_2$$

$$= xxxx - 1111 + 1111 - yy = xxx - 1111 + yy_1$$

Per seguire le regole di prima Il complemento si effettua guardando al membro con maggior numero di cifre

#### Qualche trucchetto per la complementazione

- → in generale è più facile complementare a 9(1) piuttosto che a 10(2)

- → se serve complementare a 10(2), ma ci riesce più facile complementare a 9(1) allora:

$$xxx_{10} = 1000 - xxx = 999 - xxx + 1$$

$$xxx_2 = 1000 - xxx = 111 - xxx + 1$$

→ complementiamo a 9 (o 1) quindi sommiamo 1 e otteniamo il complemento a 10 (o 2). → nella differenza si complementa al membro con maggior numero di cifre per avere più semplicità di calcolo:

$$\begin{aligned} xxxx - yy &= xxxx - 100 + 100 - yy &= \\ &= \left[ xxxx - yy_{10(2)} \right] - 100 &= zzzz - 100 \end{aligned}$$

→zzzz-100 risulta semplice ma implica sempre una sottrazione mentre dalle regolette precedenti eliminavamo solo il riporto, come si avrebbe in questo caso:

$$xxxx - yy = xxxx - 10000 + 10000 - yy =$$

$$= \left[ xxxx - yy_{10(2)} \right] - 10000 = 1zzzz - 10000$$

→ in questo modo il riporto c'è sempre →

il riporto c'è sempre →

$$xxxx < 10000 ; yy < 10000 ; xxxx > yy$$

$$\Rightarrow xxxx - yy < 10000$$

$$\Rightarrow xxxx - yy = xxxx - 10000 + 10000 - yy = 10000 + (xxxx - yy) - 10000$$

Compreso tra 10000 e 11111 (o in decimale 19999)

Sarà oggetto di altre discussioni più approfondite

... riprendiamo con l'elettronica ...

#### PERCHE' L' ELETTRONICA DIGITALE?

- più facile (dell'analogica)

- non richiede nozioni preliminari

- candidato ideale al tipo di approccio

- <u>due soli stati</u> (variaili di ingresso: tensioni)

fisici: H,L logici: T,F(1,0;).. sec. i gusti

# ✓ la logica usata:

# **ALGEBRA DI BOOLE**

- > costanti: 0,1; T,F; H,L.....

- > variabili: x,y,z.... ma ognuna ha 2 soli valori!

- ➤ funzioni: f(x,y,....) ...come sopra

- > solo 3 operazioni (fondamentali):

NOT (\_, \_\_) agisce solo su 1 var, cost. o funzione

AND (X,\*,•) agisce su 2 o più var, cost. o funzioni

OR (+) agisce su 2 o più var, cost. o funzioni

# Simboli usati

$$X \rightarrow \mathsf{NOT}$$

$$A + B \rightarrow + \rightarrow$$

OR logico e non somma algebrica

$$A \cdot B \rightarrow \cdot$$

AND logico e non prodotto algebrico

✓ saranno esplicitamente indicati i casi in cui i simboli + e · vengano essere usati come operazioni aritmetiche anzichè logiche

# **Operatori logici**

Somma (OR)

$$A+B+C+...=0$$

se tutte le var = 0

$$A+B+C+...=1$$

se almeno una var = 1

Prodotto (AND)

$$A \cdot B \cdot C \cdot ... = 0$$

se almeno una var = 0

$$A \cdot B \cdot C \cdot \dots = 1$$

se tutte le var = 1

Complemento (NOT)

$$A = 0 \rightarrow A = 1$$

$$A=1 \rightarrow \overline{A}=0$$

# **Postulati**

1)

$$A = 0$$

$o A = 1$  5)  $0 + 0 = 0$

$$2) 0 \cdot 0 = 0$$

$$3)1 \cdot 1 = 1$$

$$4)1 \cdot 0 = 0 \cdot 1 = 0$$

$$5) 0 + 0 = 0$$

6)

$$1 + 0 = 0 + 1 = 1$$

$$7) 1 + 1 = 1$$

# Proprietà & Teoremi

commutativa 1)

$$A + B = B + A$$

$A \cdot B = B \cdot A$  associativa 2)  $(A + B) + C = A + (B + C)$   $(A \cdot B) \cdot C = A \cdot (B \cdot C)$  distributiva 3)  $A \cdot (B + C) = A \cdot B + A \cdot C$   $A + (B \cdot C) = (A + B) \cdot (A + C)$  Non vale per l'algebra dei numeri reali

idempotenza 4)

$$A + A = A$$

$A \cdot A = A$

involuzione  $5$ )  $A = A$

applicazione  $\Rightarrow 6$ )  $A + (A \cdot B) = A$

$A \cdot (A + B) = A$

# Proprietà & Teoremi

#### dimostrazione

3b)

$$A + (B \cdot C) = (A + B) \cdot (A + C)$$

$(A + B) \cdot (A + C) =$

$A \cdot A + A \cdot C + A \cdot B + B \cdot C =$

$A \cdot (1 + C + B) + B \cdot C = A + B \cdot C$

dimostrazione 6a)

$$A + (A \cdot B) = A$$

6b)

$$A \cdot (A + B) = A$$

6a)

$$A + (A \cdot B) = (A + A) \cdot (A + B) =$$

6b)

$$A \cdot (A + B) = A \cdot A + A \cdot B = A + A \cdot B = A \cdot (1 + B) = A$$

identità 7 )

$$0+A=1\cdot A=A$$

dominanza 8)  $1+A=1$   $0\cdot A=0$  complementazione 9 )  $\overline{A}+A=1$   $\overline{A}\cdot A=0$  assorbimento 10 )  $A+\overline{A}B=A+B$   $A\cdot (\overline{A}+B)=A\cdot B$

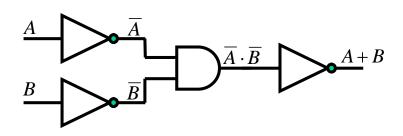

# Teorema di: DE MORGAN

11 )

$$\overline{(A + B)} = \overline{A} \cdot \overline{B}$$

$\overline{A \cdot B} = \overline{A} + \overline{B}$

# Teorema di: DE MORGAN

1)

$$\overline{A + B} = \overline{A} \cdot \overline{B}$$

2) $\overline{A \cdot B} = \overline{A} + \overline{B}$

#### Dimostrazione algebrica della 1

- Ricordiamo la proprietà  $X \cdot \overline{X} = 0$

- ponendo  $X = \overline{A} \cdot \overline{B} \Rightarrow \overline{A} \cdot \overline{B} \cdot (\overline{\overline{A} \cdot \overline{B}}) = 0$

- se è vera l'uguaglianza 1 del teorema di De Morgan allora facendo la seguente sostituzione, la precedente uguaglianza non deve cambiare:  $(\overline{A \cdot B}) = \overline{A + B} = A + B$

- •Verifichiamo quindi che  $\overline{A} \cdot \overline{B} \cdot (A+B) = 0$

$$\overline{A} \cdot \overline{B} \cdot (A + B) = \underbrace{\overline{A} \cdot A}_{=0} \cdot \overline{B} + \overline{A} \cdot \underbrace{\overline{B} \cdot B}_{=0} = 0 + 0 = 0$$

# Teorema di: DE MORGAN

#### Dimostrazione algebrica della 2

- Ricordiamo la proprietà  $X \cdot \overline{X} = 0$

- ponendo  $X = \overline{A} + \overline{B} \Longrightarrow \left(\overline{A} + \overline{B}\right) \cdot \left(\overline{\overline{A} + \overline{B}}\right) = 0$

- se è vera l'uguaglianza 2 del teorema di De Morgan allora facendo la seguente sostituzione, la precedente uguaglianza non deve cambiare:

- •Verifichiamo quindi che  $(\overline{A} + \overline{B}) \cdot (A \cdot B) = 0$

$$(\overline{A} + \overline{B}) \cdot (A \cdot B) = \underbrace{\overline{A} \cdot A}_{=0} \cdot B + A \cdot \underbrace{\overline{B} \cdot B}_{=0} = 0 + 0 = 0$$

# Significato del Teorema di DE MORGAN

✓ In generale ogni funzione booleana è una qualsiasi combinazione di operazioni logiche di base (AND, OR e NOT) fra un certo numero di variabili:

$$f(A, B, C...; +, \cdot, \overline{C}) = A \cdot (B + \overline{C}) + \overline{A \cdot \overline{C}}...$$

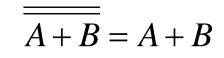

1) negando la prima uguaglianza del teorema otteniamo:

$$\overline{\overline{A+B}} = \overline{\overline{A} \cdot \overline{B}} \Rightarrow A+B = \overline{\overline{A} \cdot \overline{B}}$$

Questa uguaglianza dice che ogni OR logico può essere ottenuto con un'opportuna combinazione di AND e NOT

- → In una funzione ogni OR può essere sostituito con l'opportuna combinazione di AND e NOT

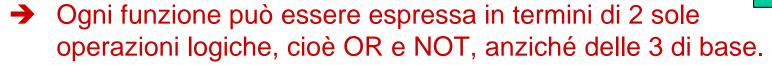

- → Ogni funzione può essere espressa in termini di 2 sole operazioni logiche, cioè AND e NOT, anziché delle 3 di base.

2) negando la seconda uguaglianza del teorema otteniamo:

$$\overline{\overline{A \cdot B}} = \overline{\overline{A} + \overline{B}} \Rightarrow A \cdot B = \overline{\overline{A} + \overline{B}}$$

Questa uguaglianza dice che ogni AND logico può essere ottenuto con un'opportuna combinazione di OR e NOT

- → In una funzione ogni AND può essere sostituito con l'opportuna combinazione di OR e NOT

- → Ogni funzione può essere espressa in termini di 2 sole operazioni logiche, cioè OR e NOT, anziché delle 3 di base.

La 1 dice che

→ Ogni funzione può essere espressa in termini di 2 sole operazioni logiche, cioè AND e NOT, anziché delle 3 di base.

La 2 dice che

1)

$$\overline{A + B} = \overline{A} \cdot \overline{B}$$

2) $\overline{A \cdot B} = \overline{A} + \overline{B}$

### Il Teorema di De Morgan dice che:

# Ogni funzione booleana può essere espressa in termini di 2 sole operazioni logiche:

$$\underline{\mathsf{AND}\,\mathsf{e}\,\mathsf{NOT}}\quad f(+,\cdot,^-) = f'(\cdot,^-)$$

### **OPPURE**

OR e NOT

$$f(+,\cdot,^-)=f'(+,^-)$$

anziché delle 3 di base AND, OR e NOT.

Vedremo in termini di circuiti il vantaggio pratico di questo teorema fondamentale.

# **FUNZIONI LOGICHE:**

si rappresentano in tabelle della verità o

con espressioni algebriche

2<sup>n</sup> combinazioni

Tutte le possibili combinazioni fra le variabili.

Date n variabili che possono assumere solo 2 valori, il numero totale di possibili combinazioni è 2<sup>n</sup>

| l | A | В | F(A,B)      |

|---|---|---|-------------|

|   | 0 | 0 | $F_1$       |

|   | 0 | 1 | $oxed{F_2}$ |

|   | 1 | 0 | $F_3$       |

|   | 1 | 1 | $F_4$       |

Valori assunti dalla funzione in corrispondenza della particolare combinazione

# **FUNZIONI LOGICHE**

• si rappresentano con tabelle di verità

$$A + B = A + \overline{A}B$$

| A | В | A + B | $\overline{A}B$ | $A + \overline{A}B$ |

|---|---|-------|-----------------|---------------------|

| 0 | 0 | 0     | 0               | 0                   |

| 0 | 1 | 1     | 1               | 1                   |

| 1 | 0 | 1     | 0               | 1                   |

| 1 | 1 | 1     | 0               | 1                   |

$$A + (B \cdot C) = (A + B) \cdot (A + C)$$

| A                          | B                               | C                          | $B \cdot C$                     | $A+(B\cdot C)$                  | A+B                             | A + C                           | $(A+B)\cdot (A+C)$              |

|----------------------------|---------------------------------|----------------------------|---------------------------------|---------------------------------|---------------------------------|---------------------------------|---------------------------------|

| 0<br>0<br>0<br>1<br>1<br>1 | 0<br>0<br>1<br>1<br>0<br>0<br>1 | 0<br>1<br>0<br>1<br>0<br>1 | 0<br>0<br>0<br>1<br>0<br>0<br>1 | 0<br>0<br>0<br>1<br>1<br>1<br>1 | 0<br>0<br>1<br>1<br>1<br>1<br>1 | 0<br>1<br>0<br>1<br>1<br>1<br>1 | 0<br>0<br>0<br>1<br>1<br>1<br>1 |

#### **Definiamo:**

| Α | В | minterm                           | maxterm                       | F     |                              |

|---|---|-----------------------------------|-------------------------------|-------|------------------------------|

| 0 | 0 | $\overline{A} \cdot \overline{B}$ | A+B                           | $F_1$ |                              |

| 0 | 1 | $\overline{A} \cdot B$            | $A + \overline{B}$            | $F_2$ | >2 <sup>n</sup> combinazioni |

| 1 | 0 | $A \cdot \overline{B}$            | $\overline{A} + B$            | $F_3$ |                              |

| 1 | 1 | $A \cdot B$                       | $\overline{A} + \overline{B}$ | $F_4$ |                              |

|   | m | i = 1                             | $M_{i} = 0$                   | )     |                              |

minterm  $(m_i)$  = prodotto fra i valori che devono assumere le variabili (negate o non) affinchè il risultato sia 1 maxterm  $(M_i)$  = somma fra i valori che devono assumere le variabili (negate o non) affinchè il risultato sia 0

Per il Teorema di De Morgan:

$$\begin{cases} m_i = \overline{M}_i \\ M_i = \overline{m}_i \end{cases} \qquad F = \sum_{i=1}^{2^n} F_i \cdot m_i = \prod_{i=1}^{2^n} (F_i + M_i)$$

#### Sviluppo di una funzione:

somma, su tutte le combinazioni delle variabili, dei prodotti fra il valore della funzione e il minterm prodotto, su tutte le combinazioni delle variabili, delle somme fra il valore della funzione e il maxterm

$$F = \sum_{i=1}^{2^{n}} F_{i} \cdot m_{i} = F = \prod_{i=1}^{2^{n}} (F_{i} + M_{i})$$

$$F = \sum_{i=1}^{2^n} F_i \cdot m_i \quad \text{in questa sommatoria contribuis cono solo i termini in cui } F = \sum_{i=1}^{2^n} F_i \cdot m_i \quad F = \sum_{i=1}^{2^n} F_i \cdot m_i \quad \text{perchè } 0 \cdot m_i = 0$$

$$F = \prod_{i=1}^{2^n} \left( F_i + M_i \right) \text{ in questa produttoria contribuiscono solo i termini in cui } F = \prod_{i=1}^{2^n} \left( F_i + M_i \right) \text{ perchè } 1 + M_i = 1$$

$$F = \sum_{i=1}^{2^{n}} F_{i} \cdot m_{i} = \prod_{i=1}^{2^{n}} (F_{i} + M_{i})$$

Dimostriamo la seguente uguaglianza:  $F = \sum_{i=1}^{2} F_i \cdot m_i = \prod_{i=1}^{2} (F_i + M_i)$

- ✓ Ammettiamo vera la prima (in seguito dimostreremo che è vera):  $F = \sum_{i=1}^{2^n} F_i \cdot m_i$

- ✓ siccome è vera la prima allora sarà anche vero che:  $\overline{F} = \sum_{i=1}^{2^n} \overline{F_i} \cdot m_i$

- ✓ Verifichiamo quindi, tramite le precedenti due relazioni, che la produttoria è uguale a F:

$$F = \prod_{i=1}^{2^n} (F_i + M_i) = \prod_{i=1}^{2^n} \overline{\overline{F_i} \cdot \overline{M_i}} = \sum_{i=1}^{2^n} \overline{F_i} \cdot \overline{M_i} =$$

$$= \sum_{i=1}^{2^n} \overline{F_i} \cdot m_i = \overline{F} = F$$

$$F = \sum_{i=1}^{2^n} F_i \cdot m_i = \prod_{i=1}^{2^n} (F_i + M_i)$$

- > serve per semplificare le funzioni (semplificabili)

- > serve per ricavare l'espressione di un funzione della quale ne conosciamo solo la tavola della verità, esempio:

| Α | В | F | m                                 | M                                                   |

|---|---|---|-----------------------------------|-----------------------------------------------------|

| 0 | 0 | 0 | $ \overline{A}\cdot\overline{B} $ | A+B                                                 |

| 0 | 1 | 1 | $\overline{A} \cdot B$            | $A + \overline{B}$                                  |

| 1 | 0 | 0 | $A \cdot \overline{B}$            | $\overline{A} + B$                                  |

| 1 | 1 | 0 | $A \cdot B$                       | $\overline{\overline{A}} + \overline{\overline{B}}$ |

# Forma "normale" di una funzione "combinatoria"

#### Somme di prodotti

$$X = \overline{A}\overline{B}\overline{C}\overline{D} + \overline{A}\overline{B}CD + \overline{A}\overline{B}\overline{C}\overline{D} + \overline{A}\overline{B}\overline{C}\overline{D} + \overline{A}\overline{B}\overline{C}D + A\overline{B}\overline{C}D + A\overline{B}\overline{C}D + A\overline{B}CD$$

$$\overline{X} = \overline{A}\overline{B}\overline{C}D + \overline{A}\overline{B}C\overline{D} + \overline{A}B\overline{C}D + \overline{A}B\overline{C}D + \overline{A}BCD + \overline{A}BCD + \overline{A}BCD + \overline{A}BCD + \overline{A}BCD + \overline{A}BCD$$

| Α | В | С | D | X | $\overline{X}$ | minterm                                 |

|---|---|---|---|---|----------------|-----------------------------------------|

| 0 | 0 | 0 | 0 | 1 | 0              | $\overline{ABCD}$                       |

| 0 | 0 | 0 | 1 | 0 | 1              | $\overline{A}\overline{B}\overline{C}D$ |

| 0 | 0 | 1 | 0 | 0 | 1              | $\overline{A}\overline{B}C\overline{D}$ |

| 0 | 0 | 1 | 1 | 1 | 0              | $\overline{A}\overline{B}CD$            |

| 0 | 1 | 0 | 0 | 1 | 0              | $\overline{A}B\overline{C}\overline{D}$ |

| 0 | 1 | 0 | 1 | 0 | 1              | $\overline{A}B\overline{C}D$            |

| 0 | 1 | 1 | 0 | 0 | 1              | $\overline{A}BC\overline{D}$            |

| 0 | 1 | 1 | 1 | 0 | 1              | $\overline{A}BCD$                       |

| 1 | 0 | 0 | 0 | 1 | 0              | $A\overline{B}\overline{C}\overline{D}$ |

| 1 | 0 | 0 | 1 | 1 | 0              | $A\overline{B}\overline{C}D$            |

| 1 | 0 | 1 | 0 | 1 | 0              | $A\overline{B}C\overline{D}$            |

| 1 | 0 | 1 | 1 | 0 | 1              | $A\overline{B}CD$                       |

| 1 | 1 | 0 | 0 | 0 | 1              | $AB\overline{CD}$                       |

| 1 | 1 | 0 | 1 | 0 | 1              | $AB\overline{C}D$                       |

| 1 | 1 | 1 | 0 | 0 | 1              | $ABC\overline{D}$                       |

| 1 | 1 | 1 | 1 | 1 | 0              | ABCD                                    |

$$X = (A + B + C + \overline{D}) \cdot (A + B + \overline{C} + D) \cdot (A + \overline{B} + C + \overline{D}) \cdot (A + \overline{B} + \overline{C} + D) \cdot (A + \overline{B} + \overline{C} + D)$$

Prodotti di Somme(si Prendono gli Zeri!!!!

A.A. 2008-09 1° trimestre Dott. M. Andreotti

Ottenuta come?

# Esempi di semplificazione:

$$F_1 = \overline{a}b + a\overline{c} + \overline{a}c + a\overline{b} = \overline{a}b + a\overline{c} + \overline{b}c$$

$$F_{1} = \overline{a}b + a\overline{c} + \overline{a}\underline{c}(\underline{b} + \overline{b}) + a\overline{b}(\underline{c} + \overline{c}) =$$

$$\overline{a}b + a\overline{c} + \overline{a}cb + a\underline{c}b + a\overline{b}c + a\overline{b}c =$$

$$\overline{a}b(1+c) + a\overline{c}(1+\overline{b}) + \overline{b}c(a+\overline{a}) =$$

$$F_{2} = \overline{a}\overline{b}c + \overline{a}b\overline{c} + \overline{a}bc + a\overline{b}c = \overline{a}\overline{c} + \overline{a}b + a\overline{b}c$$

$$F_{2} = \overline{a}\overline{b}\overline{c} + \overline{a}b\overline{c} + \overline{a}bc + a\overline{b}c = \overline{a}\overline{c}(b + \overline{b}) + \overline{a}bc + a\overline{b}c = \overline{a}\overline{c}(1 + b) + \overline{a}bc + a\overline{b}c = \overline{a}\overline{c} + \overline{a}\overline{c}b + \overline{a}bc + a\overline{b}c = \overline{a}\overline{c} + \overline{a}\overline{c}b + \overline{a}bc + a\overline{b}c = \overline{a}\overline{c} + \overline{a}b(c + \overline{c}) + a\overline{b}c$$

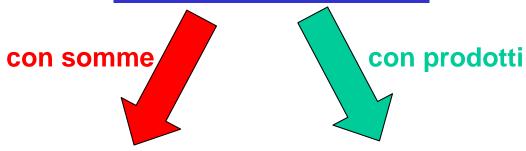

> per capire il significato dello sviluppo in minterm dobbiamo aprire un parentesi sulle basi negli spazi vettoriali

➤ base di uno spazio vettoriale: gruppo di vettori (di base) linearmente indipendenti con i quali si possono costruire tutti gli altri vettori dello spazio:

$$\sum_{i} \alpha_{i} \cdot e_{i} = 0 \iff \alpha_{i} = 0 \ \forall i$$

> esempio nel piano

$$y = P(x_p, y_p)$$

$$e_2 = X_p \times X$$

$$P = \begin{pmatrix} x_p \\ y_p \end{pmatrix} \qquad e_1 = \begin{pmatrix} 1 \\ 0 \end{pmatrix} \qquad e_2 = \begin{pmatrix} 0 \\ 1 \end{pmatrix}$$

$$P(\mathbf{x}_{p}, \mathbf{y}_{p})$$

$$P = x_{p}e_{1} + y_{p}e_{2} = x_{p}\begin{pmatrix} 1 \\ 0 \end{pmatrix} + y_{p}\begin{pmatrix} 0 \\ 1 \end{pmatrix} = \begin{pmatrix} x_{p} \\ 0 \end{pmatrix} + \begin{pmatrix} 0 \\ y_{p} \end{pmatrix} = \begin{pmatrix} x_{p} \\ y_{p} \end{pmatrix}$$

A.A. 2008-09 1° trimestre

Dott. M. Andreotti

> esempio nel spazio

$$P = x_{p}e_{1} + y_{p}e_{2} + z_{p}e_{3} = x_{p} \begin{pmatrix} 1 \\ 0 \\ 0 \end{pmatrix} + y_{p} \begin{pmatrix} 0 \\ 1 \\ 0 \end{pmatrix} + z_{p} \begin{pmatrix} 0 \\ 0 \\ 1 \end{pmatrix} = \begin{pmatrix} x_{p} \\ 0 \\ 0 \end{pmatrix} + \begin{pmatrix} 0 \\ y_{p} \\ 0 \end{pmatrix} + \begin{pmatrix} 0 \\ 0 \\ z_{p} \end{pmatrix} = \begin{pmatrix} x_{p} \\ y_{p} \\ z_{p} \end{pmatrix}$$

piano 2-dim / spazio 3-dim / spazio N-dim

$$P = \begin{pmatrix} p_1 \\ p_2 \\ p_3 \\ \vdots \\ p_n \end{pmatrix} \qquad e_1 = \begin{pmatrix} 1 \\ 0 \\ 0 \\ 0 \\ \vdots \\ 0 \end{pmatrix} \qquad e_2 = \begin{pmatrix} 0 \\ 1 \\ 0 \\ \vdots \\ 0 \end{pmatrix} \qquad e_3 = \begin{pmatrix} 0 \\ 0 \\ 1 \\ \vdots \\ 0 \end{pmatrix} \qquad \dots \qquad e_n = \begin{pmatrix} 0 \\ 0 \\ 0 \\ \vdots \\ 1 \end{pmatrix}$$

$$P = \sum_{i=1}^{n} p_i e_i = p_1 e_1 + p_2 e_2 + p_3 e_3 + \dots + p_n e_n$$

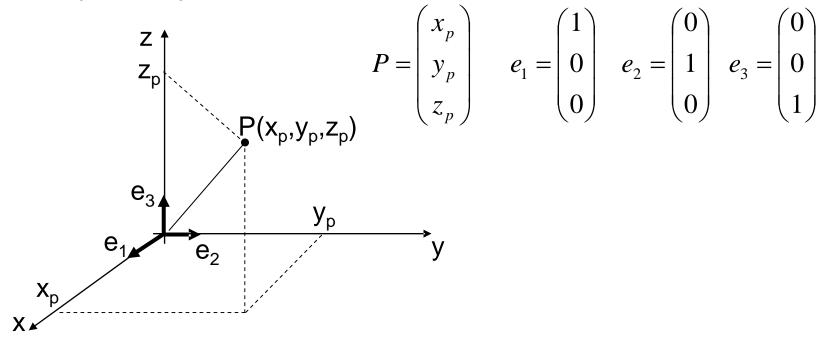

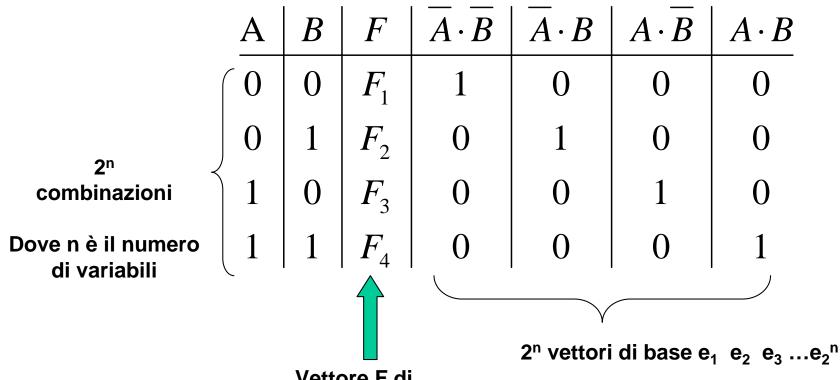

> riprendiamo lo sviluppo in minterm per una funzione di 2 variabili booleane

Vettore F di dimensione 2<sup>n</sup>

$$F = \sum_{i=1}^{2^{n}} F_{i} m_{i} = F_{1} \cdot \overline{A} \cdot \overline{B} + F_{2} \cdot \overline{A} \cdot B + F_{3} \cdot A \cdot \overline{B} + F_{4} \cdot A \cdot B$$

A.A. 2008-09 1° trimestre

➤ funzione di 3 variabili booleane – Da verificare

| A | $\boldsymbol{B}$ | C | F                          | $\overline{A} \cdot \overline{B} \cdot \overline{C}$ | $\overline{A} \cdot \overline{B} \cdot C$ | $\overline{A} \cdot B \cdot \overline{C}$ | $\overline{A} \cdot B \cdot C$ | $A \cdot \overline{B} \cdot \overline{C}$ | $A \cdot \overline{B} \cdot \overline{C}$ | $A \cdot B \cdot \overline{C}$ | $A \cdot B \cdot C$ |

|---|------------------|---|----------------------------|------------------------------------------------------|-------------------------------------------|-------------------------------------------|--------------------------------|-------------------------------------------|-------------------------------------------|--------------------------------|---------------------|

| 0 | 0                | 0 | $F_1$                      | 1                                                    | 0                                         | 0                                         | 0                              | 0                                         | 0                                         | 0                              | 0                   |

| 0 | 0                | 1 | $F_2$                      | 0                                                    | 1                                         | 0                                         | 0                              | 0                                         | 0                                         | 0                              | 0                   |

| 0 | 1                | 0 | $F_3$                      | 0                                                    | 0                                         | 1                                         | 0                              | 0                                         | 0                                         | 0                              | 0                   |

| 0 | 1                | 1 | $F_{\scriptscriptstyle 4}$ | 0                                                    | 0                                         | 0                                         | 1                              | 0                                         | 0                                         | 0                              | 0                   |

| 1 | 0                | 0 | $F_5$                      | 0                                                    | 0                                         | 0                                         | 0                              | 1                                         | 0                                         | 0                              | 0                   |

| 1 | 0                | 1 | $F_6$                      | 0                                                    | 0                                         | 0                                         | 0                              | 0                                         | 1                                         | 0                              | 0                   |

| 1 | 1                | 0 | $F_7$                      | 0                                                    | 0                                         | 0                                         | 0                              | 0                                         | 0                                         | 1                              | 0                   |

| 1 | 1                | 1 | $F_8$                      | 0                                                    | 0                                         | 0                                         | 0                              | 0                                         | 0                                         | 0                              | 1                   |

2<sup>n</sup> combinazioni

$2^n$  vettori di base  $e_1$   $e_2$   $e_3$  ... $e_2$

Vettore F di dimensione 2<sup>n</sup>

$$F = \sum_{i=1}^{2^n} F_i m_i$$

A.A. 2008-09 1° trimestre Dott. M. Andreotti

- >funzione di n variabili booleane

- √ 2<sup>n</sup> possibili combinazioni delle variabili

- ✓ quanti sono i possibili minterm che si possono costruire con n variabili?

- sono tutti i possibili prodotti delle <u>n</u> variabili prese nei 2 possibili stati (non-negato e negato) → A·B·C·D·E·... ,

Cioè è uguale al nemro delle

possibili combinazioni di n variabili prese in 2 stati (non-negato e negato) → ABCDE...

$$\Rightarrow 2^n$$

#### Modo elementare per determinare il numero delle possibili combinazioni

✓ quanti sono i possibili minterm che si possono costruire con n variabili?Contiamoli!

(si potrebbe semplicemente dire che essendo n oggetti, I quali possono assumere x valori, allora eseguendo tutti i prodotti

si ottiene che le combinazioni totali sono x<sup>n</sup>)

$$\Rightarrow \sum_{i=0}^{n-1} 2^i + 1 = 2^n$$

✓ le combinazioni che corrispondono ai numeri da 1 a  $2^n$  sono in totale  $2^n$

✓ le combinazioni che corrispondono ai numeri da 0 a  $\sum_{i=0}^{n-1} 2^i$  sono in totale  $2^n$

A.A. 2008-09 Dott. M. Andreotti 1° trimestre

➤ I minterm hanno 2<sup>n-1</sup> componenti = 0 e una sola =1

| A | В | C | $\mid F \mid$ | $\overline{A} \cdot \overline{B} \cdot \overline{C}$ | $\overline{A} \cdot \overline{B} \cdot C$ | $\overline{A} \cdot B \cdot \overline{C}$ | $\overline{A} \cdot B \cdot C$ | $A \cdot \overline{B} \cdot \overline{C}$ | $A \cdot \overline{B} \cdot \overline{C}$ | $A \cdot B \cdot \overline{C}$ | $A \cdot B \cdot C$ |

|---|---|---|---------------|------------------------------------------------------|-------------------------------------------|-------------------------------------------|--------------------------------|-------------------------------------------|-------------------------------------------|--------------------------------|---------------------|

| 0 | 0 | 0 | $F_1$         | 1                                                    | 0                                         | 0                                         | 0                              | 0                                         | 0                                         | 0                              | 0                   |

| 0 | 0 | 1 | $ F_2 $       | 0                                                    | 1                                         | 0                                         | 0                              | 0                                         | 0                                         | 0                              | 0                   |

| 0 | 1 | 0 | $F_3$         | 0                                                    | 0                                         | 1                                         | 0                              | 0                                         | 0                                         | 0                              | 0                   |

| 0 | 1 | 1 | $F_4$         | 0                                                    | 0                                         | 0                                         | 1                              | 0                                         | 0                                         | 0                              | 0                   |

| 1 | 0 | 0 | $F_{5}$       | 0                                                    | 0                                         | 0                                         | 0                              | 1                                         | 0                                         | 0                              | 0                   |

| 1 | 0 | 1 | $F_6$         | 0                                                    | 0                                         | 0                                         | 0                              | 0                                         | 1                                         | 0                              | 0                   |

| 1 | 1 | 0 | $F_7$         | 0                                                    | 0                                         | 0                                         | 0                              | 0                                         | 0                                         | 1                              | 0                   |

| 1 | 1 | 1 | $ F_8 $       | 0                                                    | 0                                         | 0                                         | 0                              | 0                                         | 0                                         | 0                              | 1                   |

➤ il minterm è quel particolare prodotto delle variabili negate/non il cui risultato vale 1 per una particolare combinazione

> quindi ogni altra combinazione corrispondente al prodotto indicato darà come risultato 0, perché tutte le altre combinazioni sono diverse da quella considerata

→ quindi sicuramente una o più delle variabili prese in quella combinazione e con quel prodotto sarà/saranno = 0, cioè il prodotto =0

- √ date n variabili → 2<sup>n</sup> possibili combinazioni

- ✓ ad ogni combinazione delle var → un termine di una funzione

- ✓ una funzione → espressa da 2<sup>n</sup> termini

→ vettore 2<sup>n</sup>-dimensionale

- ✓ con n var possiamo costruire 2<sup>n</sup> minterm

| A | В | F     | $\overline{A} \cdot \overline{B}$ | $\overline{A} \cdot B$ | $A \cdot \overline{B}$ | $A \cdot B$ |

|---|---|-------|-----------------------------------|------------------------|------------------------|-------------|

| 0 |   |       | 1                                 | 0                      | 0                      | 0           |

| 0 | 1 | $F_2$ | 0                                 | 1                      | 0                      | 0           |

| 1 |   | $F_3$ |                                   | 0                      | 1                      | 0           |

| 1 | 1 | $F_4$ | 0                                 | 0                      | 0                      | 1           |

- ✓ ogni minterm è una funzione → vettore 2<sup>n</sup>-dimensionale

- ✓ ha 2<sup>n</sup>-1 componenti nulle e 1 uguale a 1 → ottimo candidato come elemento di una base

- ✓ sono tutti diversi → sono linearmente indipendenti

- ✓I minterm costituiscono la base canonica di un ipotetico spazio vettoriale (reticolo nel caso nostro di vettori booleani) 2<sup>n</sup>-dimensionale

- ✓ Sviluppo di una funzione in minterm ↔ rappresentazione di un vettore nella base canonica

- ✓ Lo spazio vettoriale in questione è in realtà un reticolo in quanto tutti gli elementi hanno come componenti solo 0 oppure 1.

A.A. 2008-09

# **FUNZIONI LOGICHE:**

si rappresentano in tabelle della verità o

con espressioni algebriche

2<sup>n</sup> combinazioni

Tutte le possibili combinazioni fra le variabili.

Date n variabili che possono assumere solo 2 valori, il numero totale di possibili combinazioni è 2<sup>n</sup>

| A | В | F(A,B)         |

|---|---|----------------|

| 0 | 0 | $F_1$          |

| 0 | 1 | $F_2$          |

| 1 | 0 | F <sub>3</sub> |

| 1 | 1 | F <sub>4</sub> |

Valori assunti dalla funzione in corrispondenza della particolare combinazione

# FUNZIONI LOGICHE: eseguite da circuiti digitali

✓ I circuiti digitali dovranno eseguire in determinate combinazioni le operazioni logiche di base:

#### **Operatori logici**

- > Somma (OR) A+B+C+...=0 se tutte le var = 0 A+B+C+...=1 se almeno una var = 1

- Prodotto (AND) A•B•C•... = 0 se almeno una var = 0

A•B•C•... = 1 se tutte le var = 1

- > Complemento (NOT)  $A = 0 \rightarrow \overline{A} = 1$   $A = 1 \rightarrow \overline{A} = 0$

Vediamo la rappresentazione grafica di questi operatori

La rappresentazione grafica degli operatori logici è uno standard e comodità di progettazione

A.A. 2008-09

# Le operazioni ed i simboli in elettronica (digitale)

A.A. 2008-09 1° trimestre

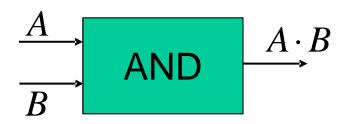

# **2) AND**

| A | $\mid B \mid$ | $A \cdot B$ |

|---|---------------|-------------|

| 0 | 0             | 0           |

| 0 | 1             | 0           |

| 1 | 0             | 0           |

| 1 | 1             | 1           |

$$A \cdot B$$

$$A_i$$

$\prod_{i=1}^n A_i$

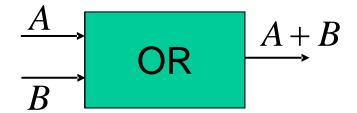

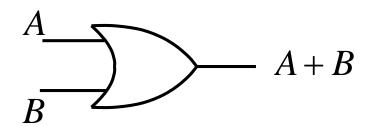

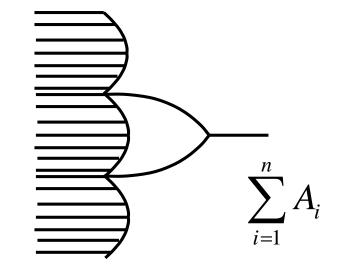

# 3) OR (inclusivo)

$$A_i$$

$\sum_{i=1}^n A_i$

$$egin{array}{c|c|c|c|c} A & B & A+B \\ \hline 0 & 0 & 0 \\ 0 & 1 & 1 \\ 1 & 0 & 1 \\ 1 & 1 & 1 \\ \hline \end{array}$$

#### Applicazione di sviluppo in minterm dell'OR

| $\underline{A}$ | B | A+B | m                                 |

|-----------------|---|-----|-----------------------------------|

| 0               | 0 | 0   | $\overline{A} \cdot \overline{B}$ |

| 0               | 1 | 1   | $A \cdot \overline{B}$            |

| 1               | 0 | 1   | $\overline{A} \cdot B$            |

| 1               | 1 | 1   | $A \cdot B$                       |

$$\begin{pmatrix} A & B & A+B & \overline{A} \cdot \overline{B} & \overline{A} \cdot B & A \cdot \overline{B} & A \cdot B \\ \hline 0 & 0 & 0 & 1 & 0 & 0 & 0 \\ 0 & 1 & 1 & 0 & 1 & 0 & 0 \\ 1 & 0 & 1 & 0 & 0 & 1 & 0 \\ 1 & 1 & 1 & 0 & 0 & 0 & 1 \end{pmatrix}$$

$$F = \sum_{i=1}^{2^{n}} F_{i} \cdot m_{i} = 0 \cdot \overline{A} \cdot \overline{B} + 1 \cdot A \cdot \overline{B} + 1 \cdot \overline{A} \cdot B + 1 \cdot A \cdot B = \left( = F = \sum_{i=1}^{2^{n}} F_{i} \cdot m_{i} \right)$$

$$= A \cdot \overline{B} + \overline{A} \cdot B + A \cdot B = A \cdot (\overline{B} + B) + \overline{A} \cdot B = A + \overline{A} \cdot B =$$

$$= (A + \overline{A}) \cdot (A + B) = A + B$$

Riprendiamo con le operazioni logiche

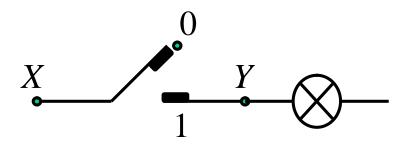

# Come li possiamo interpretare?...la preistoria

0 → interruttore aperto

1 → interruttore chiuso

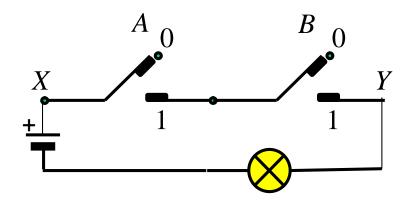

#### 2 interruttori in serie → AND logico

L' interruttore è un dispositivo a due posizioni (0,1), una delle quali determina la chiusura del contatto elettrico fra i punti X e Y mentre l'altra lascia sconnessi i due punti.

| A | $\mid B \mid$ | $\otimes$      |

|---|---------------|----------------|

| 0 | 0             | $\overline{0}$ |

| 0 | 1             | 0 > spento     |

| 1 | 0             | <b>0</b>       |

| 1 | 1             | 1 acceso       |

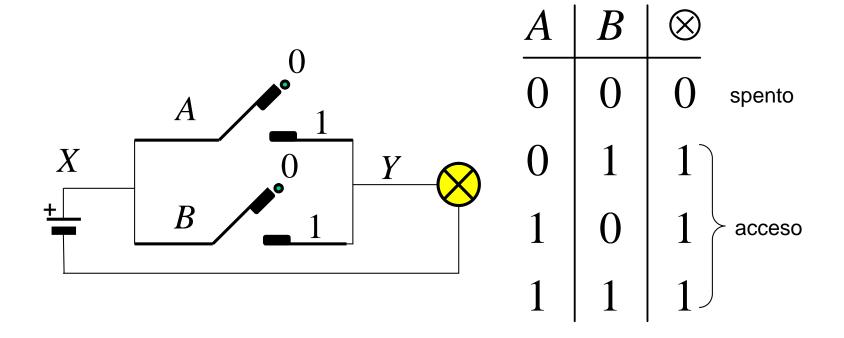

# Come li possiamo interpretare?...la preistoria

#### 2 interruttori in parallelo → OR logico

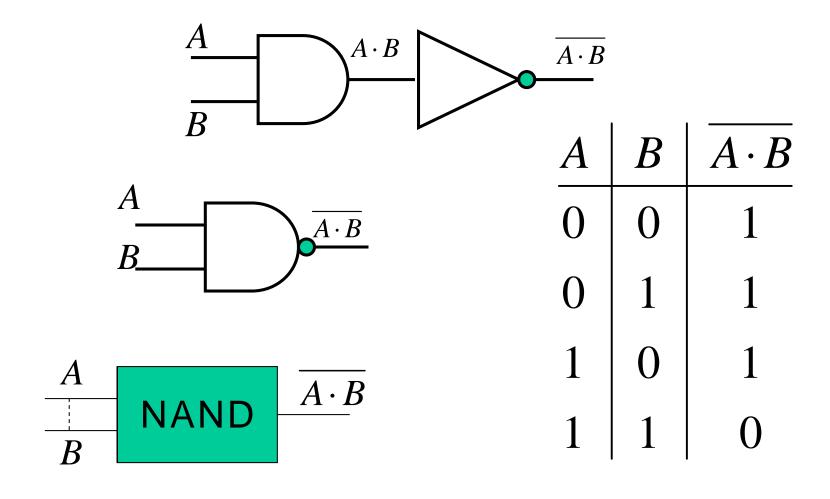

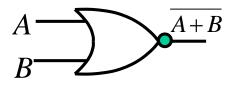

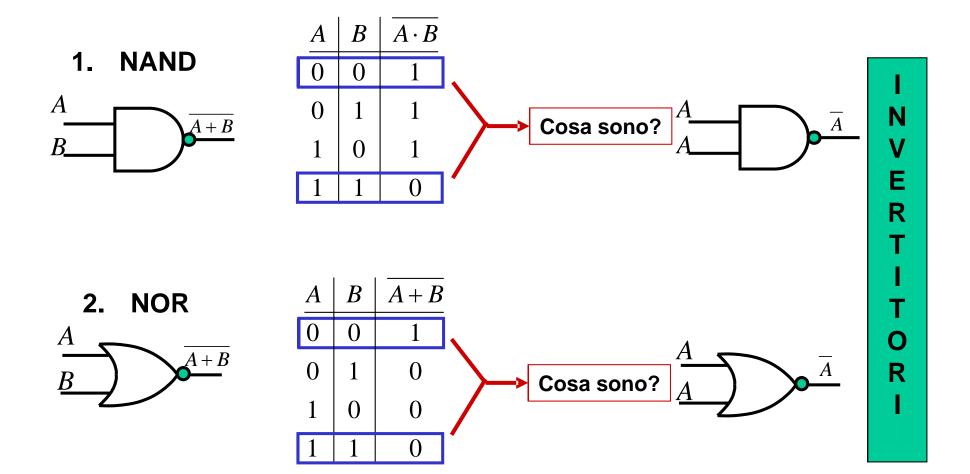

# 4) NAND (porta universale)

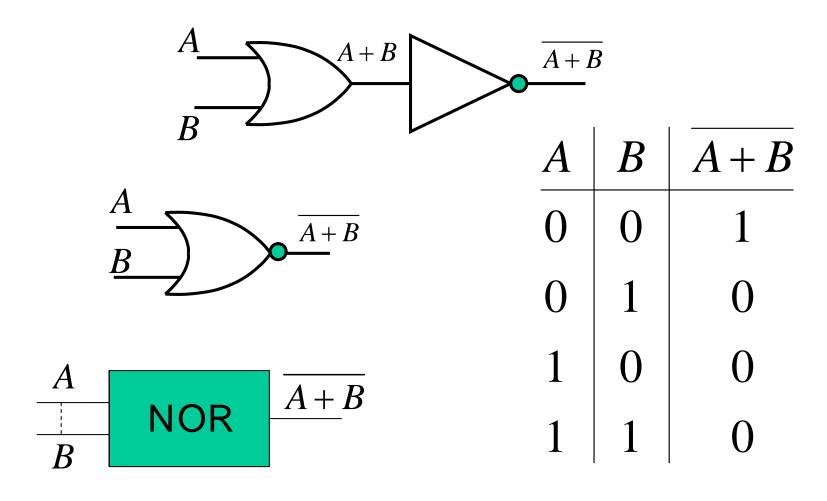

# 4) NOR (porta universale)

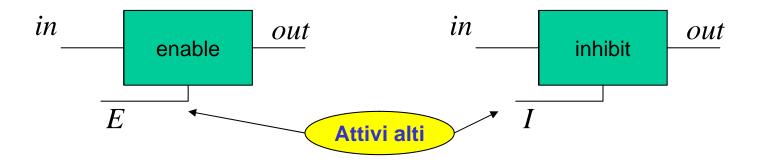

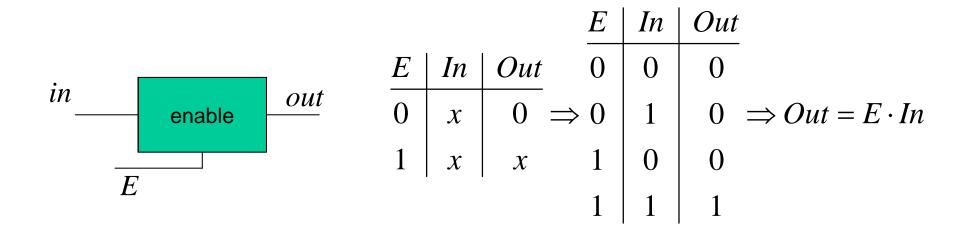

#### ... Ma esistono altri circuiti "non fondamentali"

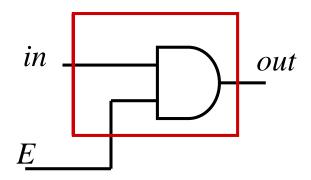

#### Enable gate (strobe):

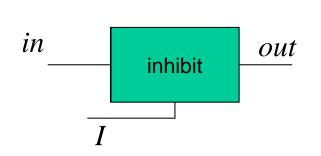

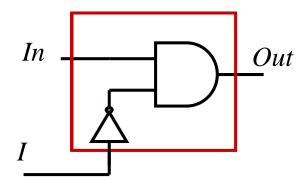

#### Inhibit gate:

Un comando attivo svolge la funzione relativa al nome del blocco!!

# Enable gate (strobe):

# Inhibit gate:

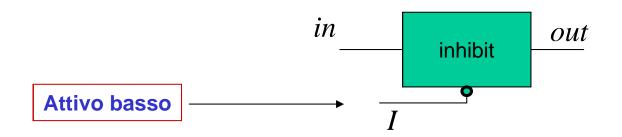

|   |    |     | I          | In | Out                                                                               |    |

|---|----|-----|------------|----|-----------------------------------------------------------------------------------|----|

| I | In | Out | 0          | 0  | 0                                                                                 |    |

| 0 | X  | x = | <b>⇒</b> 0 | 1  | $\begin{vmatrix} 1 & \Rightarrow Out = \overline{I} \cdot I \\ 0 & \end{vmatrix}$ | In |

| 1 | x  | 0   | 1          | 0  | 0                                                                                 |    |

|   |    |     | 1          | 1  | 0                                                                                 |    |

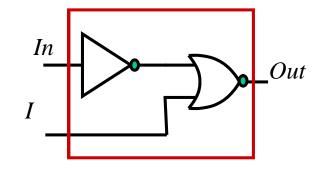

# ....e con De Morgan:

#### Altre funzioni di due variabili:

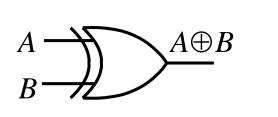

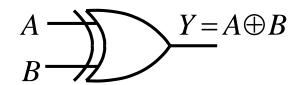

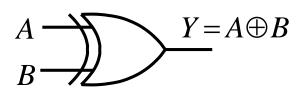

➤ OR esclusivo XOR o EXOR (si differenzia dall'OR inclusivo perché esclude tutte le combinazioni in cui le due variabili sono uguali)

| A | $\mid B \mid$ | $A \oplus B$ |

|---|---------------|--------------|

| 0 | 0             | 0            |

| 0 | 1             | 1            |

| 1 | 0             | 1            |

| 1 | 1             | 0            |

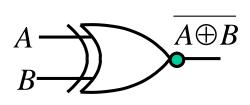

> NOR esclusivo XNOR o EXNOR (si differenzia dal NOR inclusivo perché esclude tutte le combinazioni in cui le due variabili sono diverse)

| A | B | $A \oplus B$ |

|---|---|--------------|

| 0 | 0 | 1            |

| 0 | 1 | 0            |

| 1 | 0 | 0            |

| 1 | 1 | 1            |

# Riepilogo delle funzioni viste

|--|

$$\begin{array}{c|cc} A & B & A \cdot B \\ \hline 0 & 0 & 0 \end{array}$$

$$\begin{array}{c|ccccc}

0 & 1 & 0 \\

1 & 0 & 0 \\

1 & 1 & 1

\end{array}$$

$$A \longrightarrow A + B$$

$$A \mid B \mid A + B$$

$$A \longrightarrow A \longrightarrow A \longrightarrow A \longrightarrow A \longrightarrow B$$

$$\begin{array}{c|cc} A & B & \overline{A \cdot B} \\ \hline 0 & 0 & 1 \end{array}$$

$$\begin{array}{c|cc} A & B & \overline{A+B} \\ \hline 0 & 0 & 1 \end{array}$$

$$\begin{array}{c|cccc}

0 & 1 & 0 \\

1 & 0 & 0 \\

1 & 1 & 0

\end{array}$$

$$\begin{array}{c|c|c} A & B & A \oplus B \\ \hline 0 & 0 & 0 \end{array}$$

$$egin{array}{c|c|c|c} 0 & 0 & 0 \\ 0 & 1 & 1 \\ 1 & 0 & 1 \\ 1 & 1 & 0 \\ \end{array}$$

# **EXNOR**

$$\begin{array}{c|cc} A & B & \overline{A \oplus B} \\ \hline 0 & 0 & 1 \end{array}$$

$$egin{array}{c|c|c|c} 0 & 1 & 0 \\ 1 & 0 & 0 \\ 1 & 1 & 1 \\ \end{array}$$

## Dimostriamo: Teorema di DE MORGAN

$$\overline{A + B} = \overline{A} \cdot \overline{B}$$

$$\overline{A \cdot B} = \overline{A} + \overline{B}$$

#### Dimostriamo in 2 modi diversi

- 1. Algebricamente (gia visto)

- Con le tabelle della verità

## <u>Dimostrazione 2 Teorema di De Morgan</u> *Tavole della verità*

$$\overline{A + B} = \overline{A} \cdot \overline{B}$$

$$\overline{A \cdot B} = \overline{A} + \overline{B}$$

A

B

$$X = A \cdot B$$

Complementiamo tutto!!

$C$

$D$

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

$$Y = C + D = \overline{A} + \overline{B}$$

$$Y = \overline{X} = \overline{A \cdot B} \implies \overline{A \cdot B} = \overline{A} + \overline{B}$$

$$|\overline{Y} = \overline{C + D}|$$

$$\overline{Y} = X = A \cdot B = \overline{C} \cdot \overline{D} \implies \overline{C + D} = \overline{C} \cdot \overline{D}$$

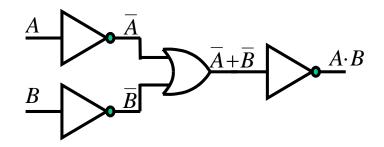

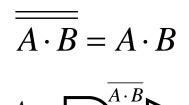

# Teorema di De Morgan → concetto di dualità

Se uno schema logico (elettronico) realizza una certa funzione, per ottenerne il complemento basta scambiare le AND con le OR (o viceversa) e complementare le variabili di ingresso

$$F = A + B$$

$$\overline{F} = \overline{A + B} = \overline{A} \cdot \overline{B}$$

$$F = A \cdot B$$

$$\overline{F} = \overline{A \cdot B} = \overline{A} + \overline{B}$$

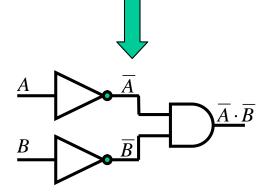

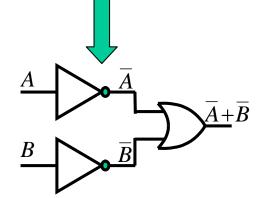

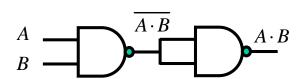

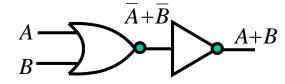

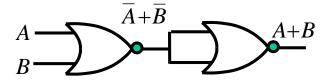

# Concetto di porte universali.....cosa vuol dire?

#### Porte universali

#### Dal teorema di De Morgan:

$$A + B = \overline{\overline{A} \cdot \overline{B}}$$

OR con solo AND e NOT  $\rightarrow$  NAND

$$A \cdot B = \overline{A} + \overline{B}$$

$\longrightarrow$  AND con solo OR e NOT  $\rightarrow$  NOR

#### Da NAND e NOR come NOT:

$$\overline{A \cdot A} = \overline{A}$$

NOT con NAND

$$\overline{A+A} = \overline{A}$$

NOT con NOR

$$\overline{A \cdot B} = A \cdot B$$

AND con NAND

$$\overline{A+B} = A+B$$

OR con NOR

AND OR e NOT→ NAND

AND OR e NOT→ NOR

Ogni circuito può essere realizzato con solo porte NAND oppure solo NOR

NAND e NOR Porte universali

#### Porte universali

#### Dal teorema di De Morgan:

$$A + B = \overline{\overline{A} \cdot \overline{B}}$$

$A \cdot B = \overline{\overline{A} + \overline{B}}$

È sufficiente realizzare il circuito corrispondente al primo membro e verificare che la sua tavola della verità sia uguale a quella del secondo membro.

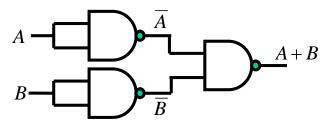

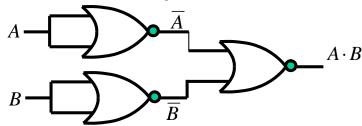

#### Or con solo porte NAND

#### **AND con solo porte NOR**

#### Porte universali

#### And con solo porte NAND

#### Or con solo porte NOR

Ogni circuito logico può essere costruito con solo porte NAND oppure con solo porte NOR

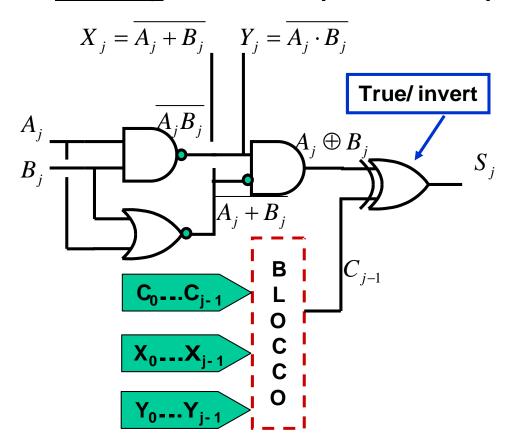

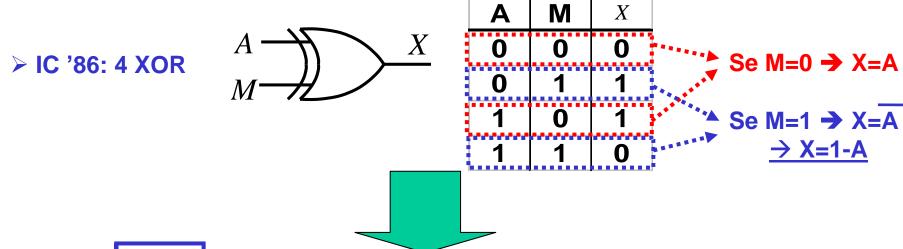

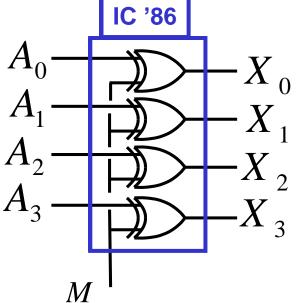

#### La Funzione True/Invert

Usando la variabile B come bit di controllo in un XOR otteniamo un blocco che esegue la funzione True/Invert:

- se B=0 il blocco riporta in uscita la variabile d'ingresso (True)

- se B=1 il blocco riporta in uscita la variabile d'ingresso negata (Invert)

| В | A | $A \oplus B$ |

|---|---|--------------|

| 0 | 0 | 0            |

| 0 | 1 | 1            |

| 1 | 0 | 1            |

| 1 | 1 | 0            |

E' uguale alla OR tranne che vale zero se A=B=1.Quindi:

è vera se : è vera

$$(A + B)$$

ded è falsa  $A \cdot B$

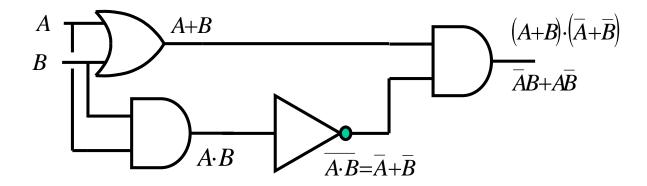

$$XOR(A,B) = (A+B) \cdot \overline{AB}$$

# 4 porte di base (non universali)

| В | A | $A \oplus B$ |

|---|---|--------------|

| 0 | 0 | 0            |

| 0 | 1 | 1            |

| 1 | 0 | 1            |

| 1 | 1 | 0            |

# Sviluppo minterm

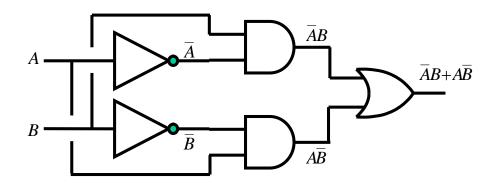

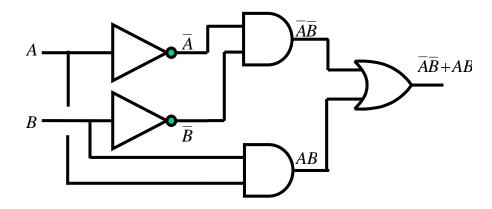

$$A \oplus B = \overline{A}B + A\overline{B}$$

## Sviluppo maxterm

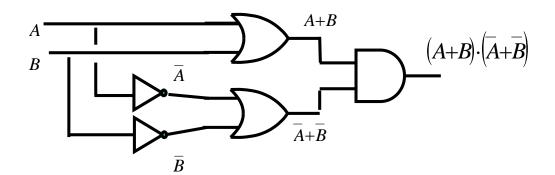

$$A \oplus B = (A+B) \cdot (\overline{A} + \overline{B})$$

# Ma sono 5 porte! E si può migliorare.....con: De Morgan

## Con De Morgan e qualche trucco... otteniamo XOR con 4 porte

$$A \oplus B = \overline{A}B + A\overline{B} = \overline{\overline{A}B} \cdot \overline{A}\overline{\overline{B}}$$

$$\overline{\overline{A}B} = \overline{\overline{A}B} + B\overline{\overline{B}} = \overline{B}(\overline{\overline{A}} + \overline{\overline{B}}) = \overline{B}\overline{\overline{A}B}$$

$$\overline{\overline{A}B} = \overline{A}\overline{\overline{B}} + A\overline{\overline{A}} = \overline{A}(\overline{\overline{A}} + \overline{\overline{B}}) = \overline{A}\overline{\overline{A}B}$$

$$\Rightarrow A \oplus B = \overline{\overline{A}\overline{\overline{A}B}} \cdot \overline{\overline{B}\overline{\overline{A}B}}$$

$$A \oplus B = \overline{\overline{A}\overline{\overline{A}B}} \cdot \overline{\overline{B}\overline{\overline{A}B}}$$

Si poteva arrivare a questo risultato con qualche metodo sistematico? La risposta non è banale, vedremo...

| В | Α | $\overline{A \oplus B}$ |

|---|---|-------------------------|

| 0 | 0 | 1                       |

| 0 | 1 | 0                       |

| 1 | 0 | 0                       |

| 1 | 1 | 1                       |

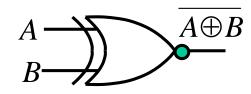

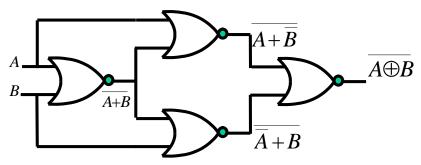

# Ma sono 5 porte! E si può migliorare.....con: De Morgan

La funzione vale 1 solo se A=B ( funzione di eguagianza e complemento della XOR). Per De Morgan il complemento si ottiene: <u>scambiando le AND con le OR e complementando le variabili di ingresso.</u> In questo caso però l'ultima operazione di complementazione non modifica la tavola della verità:

$$XNOR(A,B) = XNOR(\overline{A},\overline{B})$$

per cui è sufficiente scambiare le AND con le OR:

Dott. M. Andreotti

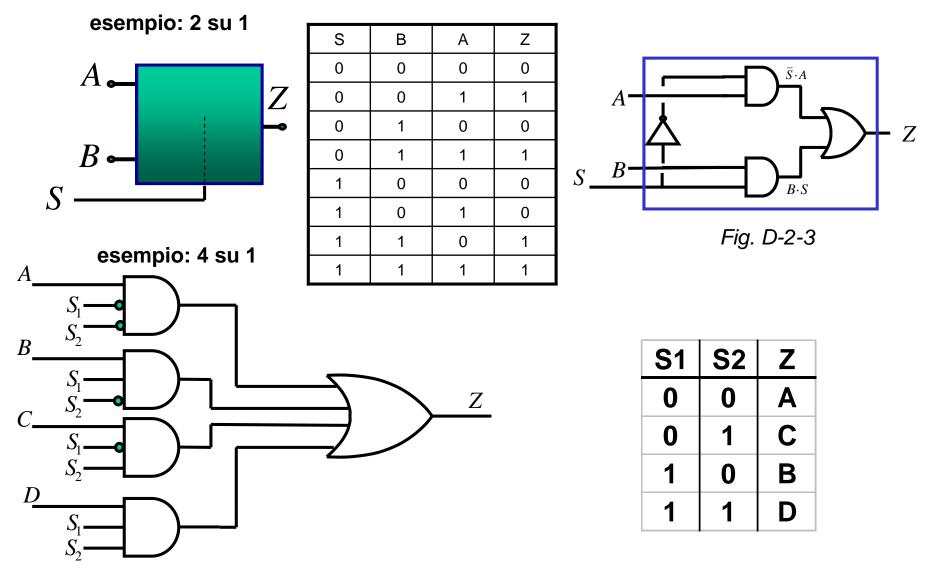

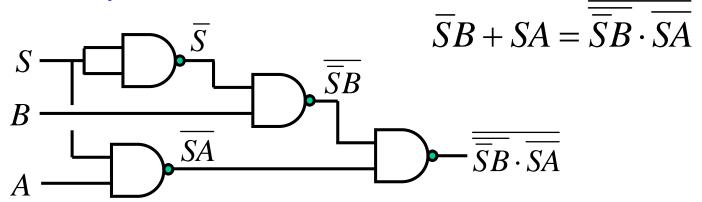

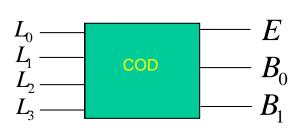

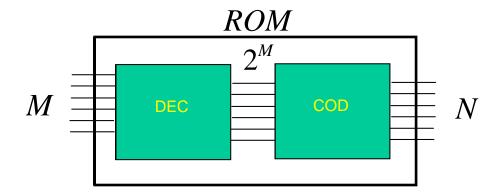

# Multiplexers (smistatore): smista l'ingresso selezionato in uscita

| S | Α | В | Y |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 |

| S | Α | В | Y |

|---|---|---|---|

| 0 | X | X | В |

| 1 | X | X | A |

S = bit di selezione, la variabile d'uscita sarà uguale all'ingresso A o B come deciso dal bit S

2 bit se le var da smistare sono da 2 a 4  $\rightarrow$  S<sub>1</sub>S<sub>2</sub> =00, 01, 10, 11

In generale per smistare N variabili serve un selettore che possa assumere N combinazioni  $\rightarrow N=2^{nbit} \rightarrow nbit = log_2N$

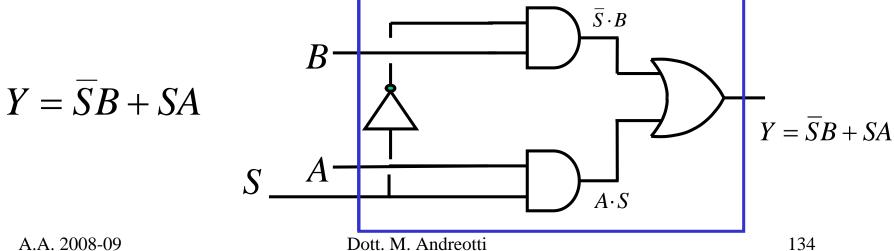

# Multiplexers a due ingressi

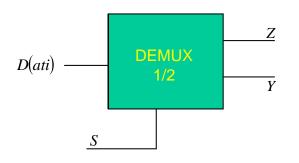

COME PREVEDIBILE ABBIAMO UNA SOLA FUNZIONE LOGICA:

$$Y = \overline{A}B\overline{S} + AB\overline{S} + A\overline{B}S + ABS$$

| _   |                   |    | ~ |

|-----|-------------------|----|---|

|     |                   |    |   |

| Y = | $=\overline{S}B+$ | SA |   |

S

В

Α

Υ

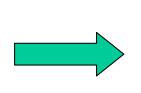

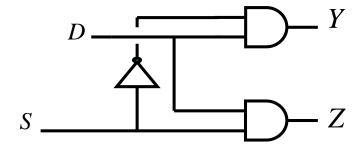

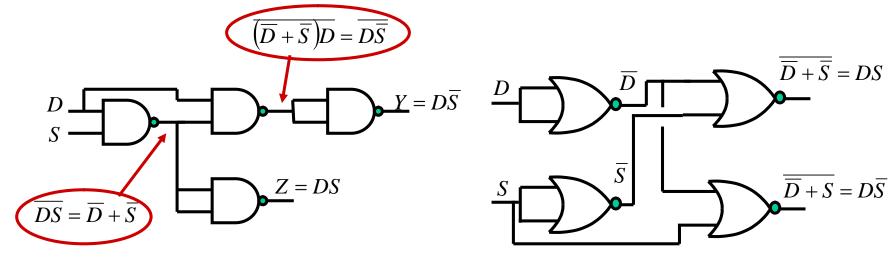

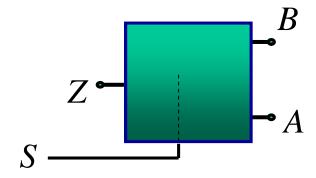

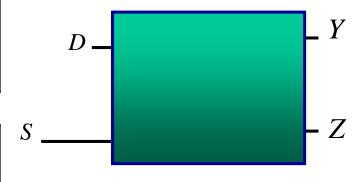

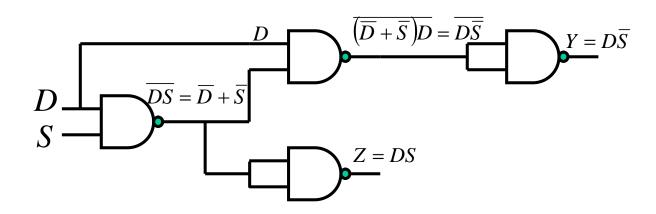

# **DeMultiplexers (smistatore)**: smista l'ingresso nell'uscita selezionata

| S | D | Z | Υ |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 1 | 0 | 1 |

| 1 | 0 | 0 | 0 |

| 1 | 1 | 1 | 0 |

| S | D | Z | Y |

|---|---|---|---|

| 0 | х | 0 | D |

| 1 | Х | D | 0 |

Numero di uscite da gestire e numero di bit di selezione: analogo al multiplexer

COME PREVEDIBILE ABBIAMO DUE FUNZIONI LOGICHE:

$$Z = \underline{S}D$$

$$Y = \overline{S}D$$

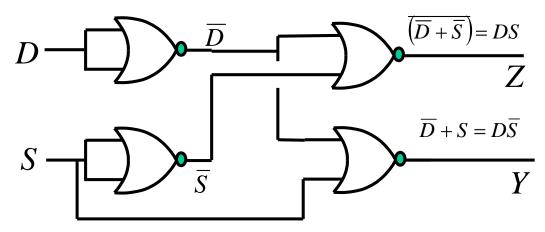

# **Comparatore**

| Α | В | A <b< th=""><th>A=B</th><th>A&gt;B</th></b<> | A=B | A>B |

|---|---|----------------------------------------------|-----|-----|

| 0 | 0 | 0                                            | 1   | 0   |

| 0 | 1 | 1                                            | 0   | 0   |

| 1 | 0 | 0                                            | 0   | 1   |

| 1 | 1 | 0                                            | 1   | 0   |

#### Partiamo dal caso più semplice a 1 bit:

COME PREVEDIBILE ABBIAMO TRE FUNZIONI LOGICHE:

A.A. 2008-09 1° trimestre

Dott. M. Andreotti

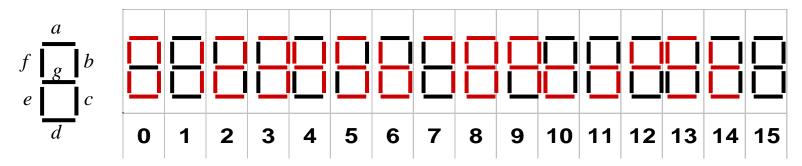

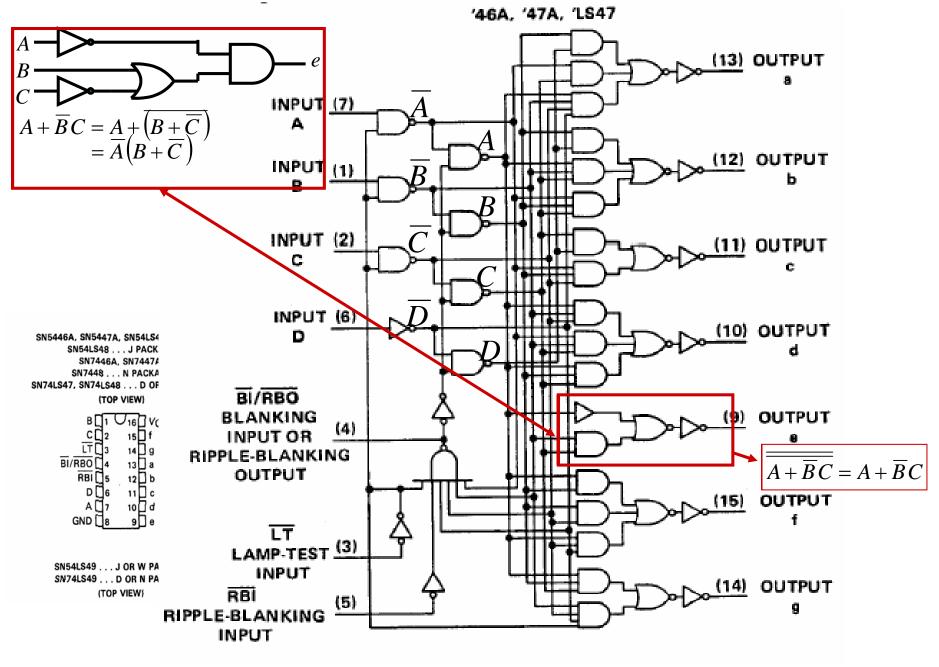

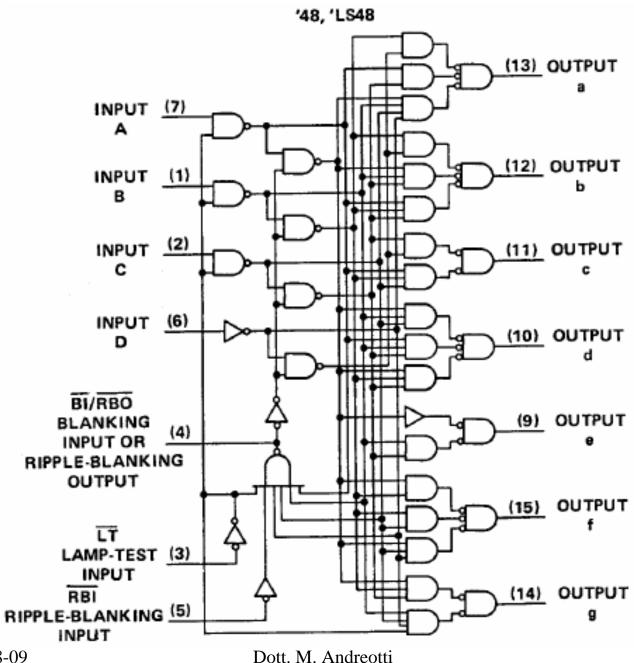

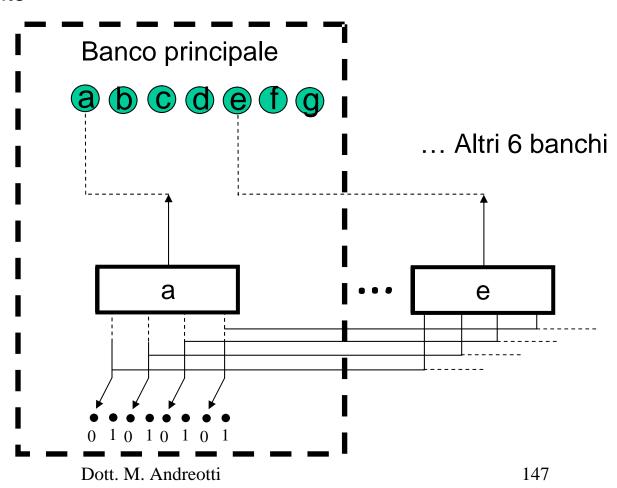

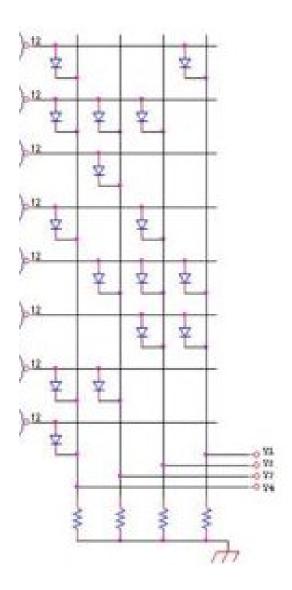

# Convertitore BCD-7 segmenti

$\begin{array}{c|c}

a \\

f \mid g \mid b \\

e \mid c \mid c

\end{array}$

7 segmenti: è un tipo di display

-- Dobbiamo rappresentare i numeri da 0 a 9: di quanti bit abbiamo bisogno?

$$N_{bit} = log_2 10 = 3.32 = 4 bit$$

-- Ogni segmento è una funzione dei 4 bit >

'46A, '47A, 'LS47 FUNCTION TABLE (T1)

| DECIMAL<br>OR | INPUTS |     |     | BI/RBO† | OUTPUTS |    |     |     |     | NOTE |     |     |     |     |     |

|---------------|--------|-----|-----|---------|---------|----|-----|-----|-----|------|-----|-----|-----|-----|-----|

| FUNCTION      | LT     | RBI | D   | С       | В       | Α  |     | а   | ь   | С    | d   | е   | f   | g   |     |

| 0             | н      | н   | L   | L       | L       | L  | н   | ON  | ON  | ON   | ON  | ON  | ON  | OFF |     |

| 1             | н      | ×   | L   | L       | L       | н  | н   | OFF | ON  | ON   | OFF | OFF | OFF | OFF |     |

| 2             | н      | ×   | L   | L       | н       | Ł  | н   | ON  | ON  | OFF  | ON  | ON  | OFF | ON  |     |

| 3             | _ н    | ×   | L   | L       | н       | н  | н   | ON  | ON  | ON   | ON  | OFF | OFF | ON  |     |

| 4             | Н      | ×   | L   | н       | L       | L  | н   | OFF | ON  | ON   | OFF | OFF | ON  | ON  |     |

| 5             | н      | ×   | L   | н       | L       | н  | н   | ON  | OFF | ON   | ON  | OFF | ON  | ON  |     |

| 6             | н      | [ × | L   | н       | н       | Ĺ  | ) # | OFF | OFF | ON   | ON  | ON  | ON  | ON  | 1   |

| 7             | н      | ×   | L_  | н       | н       | н  | н   | ON  | ON  | ON   | OFF | OFF | OFF | OFF | , 1 |

| 8             | н      | ×   | Н   | L       | L       | L  | н   | ON  | ON  | ON   | ON  | ON  | ON  | ON  | '   |

| 9             | н      | ×   | н   | L       | L       | н  | н   | ON  | ON  | ON   | OFF | OFF | ON  | ON  |     |

| 10            | н      | ×   | н   | L       | н       | L  | н   | OFF | OFF | OFF  | ON  | ON  | OFF | ON  |     |

| 11            | н      | ×   | Н   | L       | н       | Н. | н   | OFF | OFF | ON   | ON  | OFF | OFF | ON  |     |

| 12            | +      | X   | н   | н       | L       | L  | н   | OFF | ON  | OFF  | OFF | OFF | ON  | ON  |     |

| 13            | н      | ×   | н   | н       | L       | н  | н   | ON  | OFF | OFF  | ON  | OFF | ON  | ON  | } , |

| 14            | н      | ×   | н   | н       | н       | L  | н   | OFF | OFF | OFF  | ON  | ON  | ON  | ON  |     |

| 15            | н      | ×   | .н  | н       | н       | н  | н   | OFF | OFF | OFF  | OFF | OFF | OFF | OFF |     |

| 81            | ×      | ×   | ×   | ×       | ×       | ×  | L   | OFF | OFF | OFF  | OFF | OFF | OFF | OFF | 2   |

| RBI           | н      | L   | L   | L       | L       | L  | L   | OFF | OFF | OFF  | OFF | OFF | OFF | OFF | 3   |

| LT_           | L      | ×   | L × | ×       | ×       | ×  | н   | ON  | ON  | ON   | ON  | ON  | ON  | ON  | 4   |

H = high level, L ≈ low level, X = irrelevant

NOTES: 1. The blanking input (Bi) must be open or held at a high logic level when output functions 0 through 15 are desired. The ripple-blanking input (유럽) must be open or high if blanking of a decimal zero is not desired.

- 2. When a low logic level is applied directly to the blanking input (BI), all segment outputs are off regardless of the level of any other input.

- 3. When ripple-blanking input (RBI) and inputs A, B, C, and D are at a low level with the lamp test input high, all segment outputs go off and the ripple-blanking output (RBO) goes to a low level (response condition).

- When the blanking input/ripple blanking output (BI/RBO) is open or held high and a low is applied to the lamp-test input, all segment outputs are on.

1BI/RBO is wire AND logic serving as blanking input (BI) and/or ripple-blanking output (RBO).

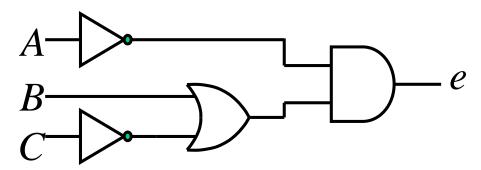

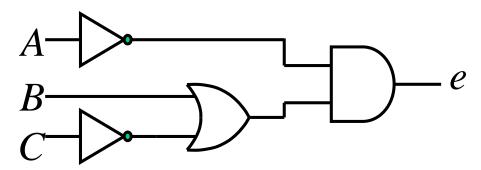

#### Consideriamo il segmento e......

....e semplifichiamo la funzione!

$$e = \overline{A}\overline{C}\overline{D}(B + \overline{B}) + \overline{A}BC(D + \overline{D}) + \overline{A}\overline{C}D(B + \overline{B})$$

$$= \overline{A}\overline{C}D + \overline{A}BC + \overline{A}\overline{C}D = \overline{A}\overline{C}(D + D) + \overline{A}BC$$

....poi si ricorre ad un trucco:

$$e = \overline{A}\overline{C} + \overline{A}BC = \overline{A}\overline{C}(1+B) + \overline{A}BC$$

$$= \overline{A}\overline{C} + \overline{A}BC + \overline{A}BC = \overline{A}\overline{C}(1+B) + \overline{A}BC$$

$$= \overline{A}\overline{C} + \overline{A}BC + \overline{A}BC = \overline{A}\overline{C}(1+B) + \overline{A}BC$$

A.A. 2008-09 1° trimestre

Dott. M. Andreotti

A.A. 2008-09 1° trimestre

Dott. M. Andreotti

## **Introduzione a CircuitMaker – qualche immagine**

## Introduzione a CircuitMaker – qualche immagine

## **Introduzione a CircuitMaker – qualche immagine**

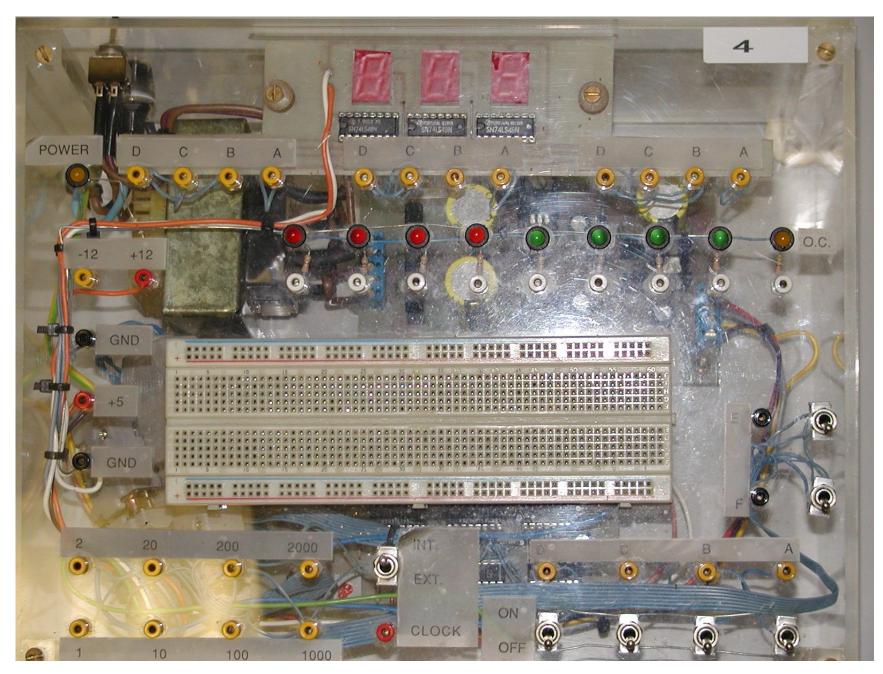

# Attività di Laboratorio ELETTRONICA DEI SISTEMI DIGITALI Parte I

Corso di Laurea in Informatica e TFI Anno Accademico 2007-2008

# Scopo del Laboratorio di Elettronica Digitale

Circuiti: Analogici, Logici

sottosistemi a componenti: Discreti, Integrati

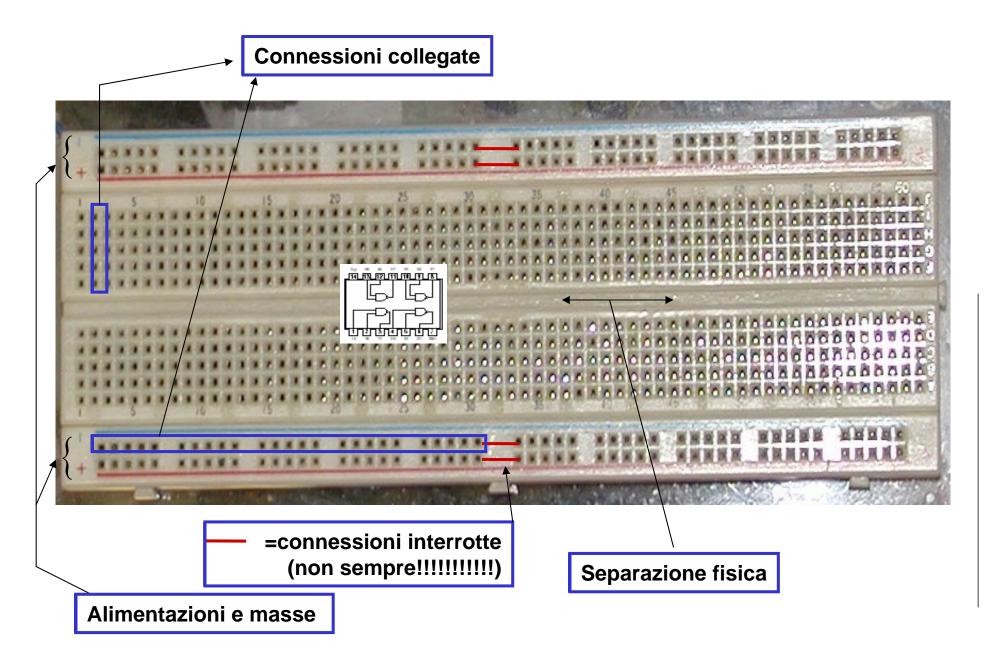

Realizzazioni di prototipi: uso delle breadboard

Circuiti Integrati: chip monolitici

Due grossi gruppi:

- gruppo bipolare: cariche positive e negative

- gruppo unipolare: cariche di una sola polarità

I gruppi si dividono in famiglie

Le famiglie sono caratterizzate da caratteristiche salienti All' interno delle famiglie i CI sono tutti compatibili tra loro

- Stessi livelli

- Stesse alimentazioni

- Potenze compatibili

Tra famiglie diverse i CI sono (in generale) incompatibili tra loro

### Circuiti di interfaccia

I principali parametri che caratterizzano le famiglie:

- 1. Ritardo di propagazione:maggiore nei circuiti unipolari

- 2. Dissipazione di potenza:inferiore negli unipolari

- 3. Capacità di pilotaggio (fan-out):maggiore negli unipolari

- 4. Immunità al rumore: migliore negli unipolari

- 5. Capacità di una porta (fan-in): equivalente

- 6. Densità di integrazione:maggiore negli unipolari

La scelta va fatta in base alle caratteristiche/necessità di progetto

### Famiglie Bipolari:

- 1. RTL:obsoleta

- 2. DTL:obsoleta

- 3. HTL:

- 4. TTL standard:

- 5. TTL a bassa dissipazione:

- 6. TTL high speed:

- 7. TT Schottky:

- 8. ECL:

- 9. I<sup>2</sup>L:

### Famiglie unipolari:

- 1. P-MOS H.V.:

- P-MOS L.V.:

- 3. N-MOS:

- 4. C-MOS:

### Scale di Integrazione:

- S(mall)S(cale)I(ntegration):

12 porte (50 transistor equivalenti)

- 2. M(edium)S(cale)I(tegration): 12-100 porte (50-500 trs equivalenti)

- 3. L(arge)S(cale)I(ntegration): 100-1000 porte (500-4000 trs equivalenti)

- V(ery)L(arge)S(cale)I(ntegration):

>1000 porte (≥ 10<sup>7</sup> trs eq. per il PENTIUM INTEL nel 2002)

#### TI LOGIC DEVICE NOMENCLATURE

Are you confused by the device names and numbers of logic products? Do you need to know if a part has bus hold or series damping resistors? What kind of package the part is available in? The table below takes the mystery out of what all the letters and numbers in TI standard catalog logic devices represent. Take your favorite TI logic part number and find out what it can do.

| SN | 74 | LVC | Н | 16 | 2 | 244 | A   | $\mathbf{DGG}$ | R  |

|----|----|-----|---|----|---|-----|-----|----------------|----|

| 11 | 2  | 3   | 4 | 5  | 6 | .7  | . 8 | 9:             | 10 |

#### 1. Standard Prefix

Example: SNJ - Conforms to MIL-PRF-38535 (QML)

#### 2. Temperature Range

- o 54 Military

- O 74 Comercial

#### 3. Family

#### 4. Special Features

- O Blank = No Special Features

- o C Configurable Vcc (LVCC)

- D <u>Level-Shifting Diode</u> (CBTD)

- O H Bus Hold (ALVCH)

- o K Undershoot-Protection Circuitry (CBTK)

- R <u>Damping Resistor on Inputs/Outputs</u> (LVCR)

- o S Schottky Clamping Diode (CBTS)

- o Z Power-Up 3-State (LVCZ)

#### 5. Bit Width

- o Blank = Gates, MSI, and Octals

- O 1G Single Gate

- o 8 Octal IEEE 1149.1 (JTAG)

- o 16 Widebus™ (16, 18, and 20 bit)

- o 18 Widebus IEEE 1149.1 (JTAG)

- O 32 Widebus+™(32 and 36 bit)

### Dott M And

### o 25 - 25-ohm Line Driver 7. Function

o Blank = No Options

o 4 - Level Shifter

o 244 - Noninverting Buffer/Driver

O 2 - Series-Damping Resistor on Outputs

- o 374 D-Type Flip-Flop

- O 573 D-Type Transparent Latch

- o 640 Inverting Transceiver

#### 8. Device Revision

- o Blank = No Revision

- Letter Designator A-Z

#### Packages

6. Options

- D, DW Small-Outline Integrated Circuit (SOIC)

- o DB, DL Shrink Small-Outline Package (SSOP)

- o DBB, DGV Thin Very Small-Outline Package (TVSOP)

- o DBQ Quarter-Size Outline Package (QSOP)

- o DBV, DCK Small-Outline Transistor Package (SOT)

- o DGG, PW Thin Shrink Small-Outline Package (TSSOP)

- o FK Leadless Ceramic Chip Carrier (LCCC)

- o FN Plastic Leaded Chip Carrier (PLCC)

- o GB Ceramic Pin Grid Array (CPGA)

- O GKE, GKF MicroStar BGA<sup>™</sup> Low-Profile Fine-Pitch Ball Grid Array (LFBGA)

- O GQL, GQN MicroStar Junior BGA Very-Thin-Profile Fine-

### Pitch Ball Grid Array (VFBGA)

- O HFP, HS, HT, HV Ceramic Quad Flat Package (CQFP)

- O J, JT Ceramic Dual-In-Line Package (CDIP)

- O N, NP, NT Plastic Dual-In-Line Package (PDIP)

- o NS, PS Small Outline Package (SOP)

- PAG, PAH, PCA, PCB, PM, PN, PZ Thin Quad Flat Package (TQFP)

- PH, PQ, RC Quad Flat Package (QFP)

- O W, WA, WD Ceramic Flat Package (CFP)

### 10. Tape and Reel

All new or changed devices in the **DB** and **PW** package types include the **R** designation for reeled product. Existing products designated as **LE** presently maintain that designation, but will be converted to **R** in the future.

#### Nomenclature Examples:

- For an Existing Device SN74LVTxxxDBLE

- For a New or Changed Device SN74LVTxxxADBR

- o LE Left Embossed (valid for DB and PW packages only)

- R Standard (valid for all surface-mount packages except existing DB and PW devices)

### Family Comparison

The table below compares some typical characteristics of several popular logic families available in the market today. The following sections provide brief explanations of the various parameters.

| Typical                                  |                    |                    |                    |                    |                 | Logi           | ic Fami            | lies             |                |                    |                    |                    |                    |

|------------------------------------------|--------------------|--------------------|--------------------|--------------------|-----------------|----------------|--------------------|------------------|----------------|--------------------|--------------------|--------------------|--------------------|

| Commercial                               |                    | Т                  | TIL                |                    |                 | 1              | CMOS               |                  |                |                    | E                  | CL                 |                    |

| Parameter<br>(0°C to +70°<br>C)          | LS                 | ALS                | АВТ                | FAST               | MG              | нС             | FACT               | LVC              | LCX            | 10H                | 100K               | ECL<br>in<br>PS(3) | E-<br>Lite         |

| Speed<br>Gate Prop<br>Delay (ns)         | 9                  | 7                  | 2.7                | 3                  | 65              | 8              | 5                  | 3.3              | 3.5            | 1                  | 0.75               | 0.33               | 0.22               |

| Flip-Flop<br>Toggle Rate<br>(MHz)        | 33                 | 45                 | 200                | 125                | 4               | 45             | 160                | 200              | 200            | 330                | 400                | 1,000              | 2800               |

| Output Edge<br>Rate (ns)                 | 6                  | 3                  | 3                  | 2                  | 50              | 4              | 2                  | 3.7              | 3.6            | 1                  | 0.7                | 0.5                | 0.25               |

| Power<br>Consumption<br>Per Gate<br>(mW) |                    |                    |                    |                    |                 |                |                    |                  |                |                    |                    |                    |                    |

| Quiescent                                | 5                  | 1.2                | 0.005              | 12.5               | 0.0006          | 0.003          | 0.0001             | 0.003            | 1E-<br>04      | 25                 | 50                 | 25                 | 73                 |

| Operating (1<br>MHz)                     | 5                  | 1.2                | 1.0                | 12.5               | 0.04            | 0.6            | 0.6                | 0.8              | 0.3            | 25                 | 50                 | 25                 | 73                 |

| Supply<br>Voltage (V)                    | +4.5<br>to<br>+5.5 | +4.5<br>to<br>+5.5 | +4.5<br>to<br>+5.5 | +4.5<br>to<br>+5.5 | +3<br>to<br>+18 | +2<br>to<br>+6 | +1.2<br>to<br>+3.6 | +2<br>to<br>+3.6 | +2<br>to<br>+6 | -4.5<br>to<br>-5.5 | -4.2<br>to<br>-4.8 | -4.2<br>to<br>-5.5 | -4.2<br>to<br>-5.5 |

| Output Drive<br>(mA)                     | 8                  | 8                  | 32/64              | 20                 | 1               | 4              | 24                 | 24               | 24             | 50<br>ohm<br>load  | 50<br>ohm<br>load  | 50<br>ohm<br>load  | 50<br>ohm<br>load  |

A.A. 2008-09 Dott. M. Andreotti 112

A.A. 2008-09 1° trimestre

Dott. M. Andreotti

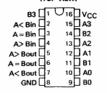

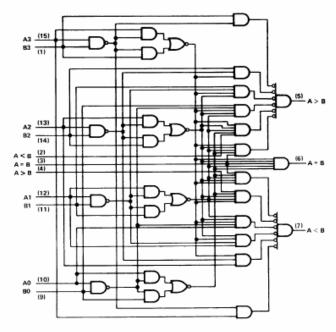

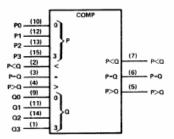

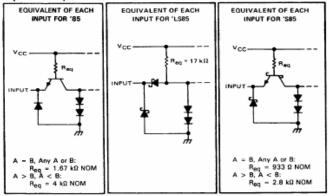

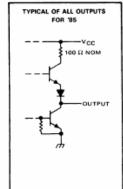

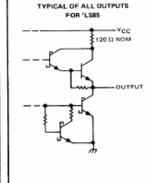

SN5485, SN54LS85, SN54S85 SN7485, SN74LS85, SN74S85 4-BIT MAGNITUDE COMPARATORS

| TYPE        | TYPICAL<br>POWER<br>DISSIPATION | TYPICAL<br>DELAY<br>(4-BIT WORDS) |

|-------------|---------------------------------|-----------------------------------|

| '85         | 275 mW                          | 23 ns                             |

| 1.885       | 52 mW                           | 24 ns                             |

| <b>'S85</b> | 365 mW                          | 11 ns                             |

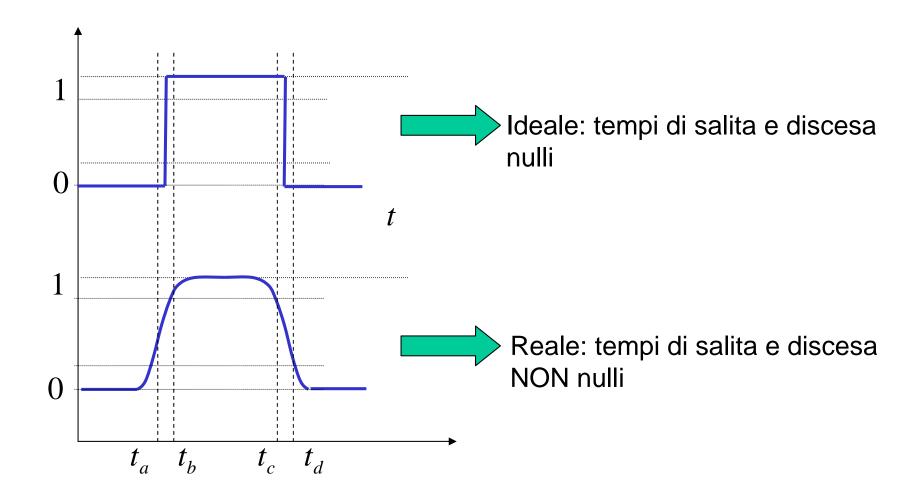

#### description