## Temporizzazioni nell'interfacciamento

## Temporizzazioni nell'interfacciamento (2)

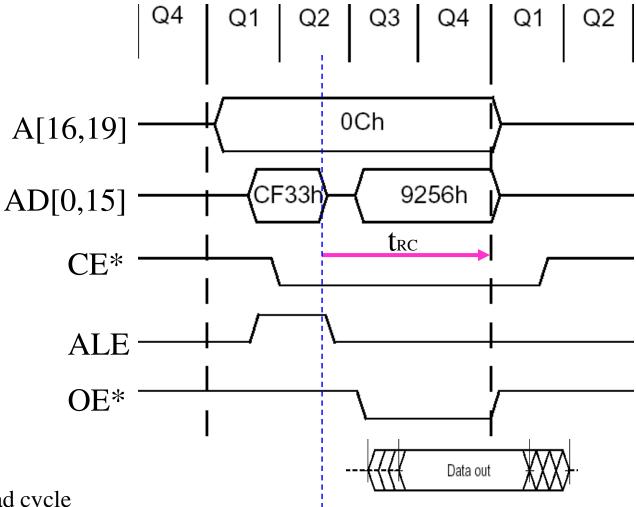

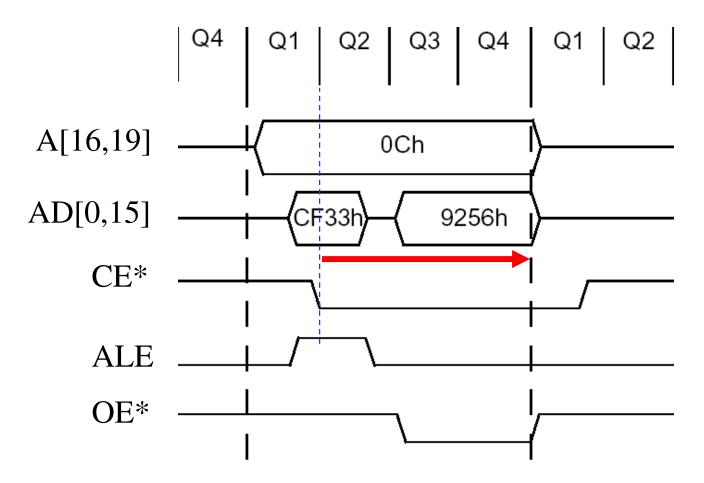

#### Ciclo di Data Read

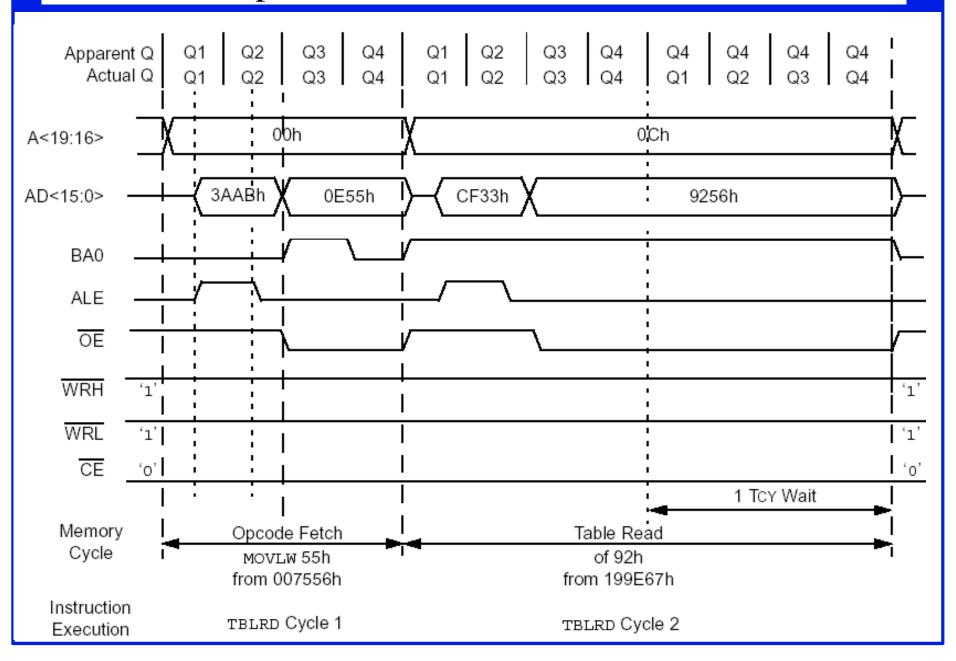

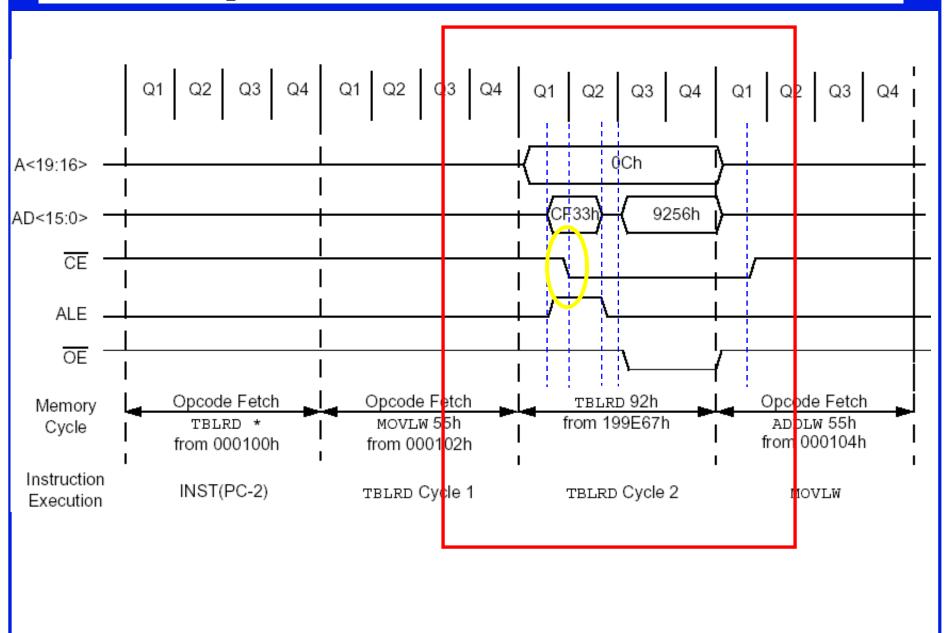

## Temporizzazioni nell'interfacciamento (micro)

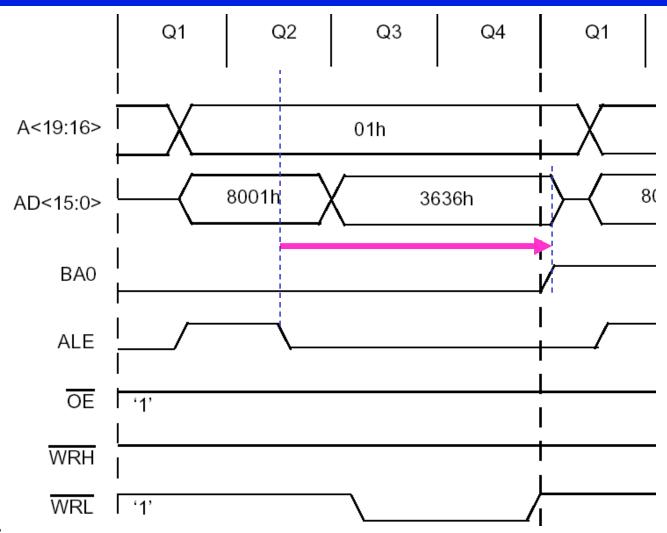

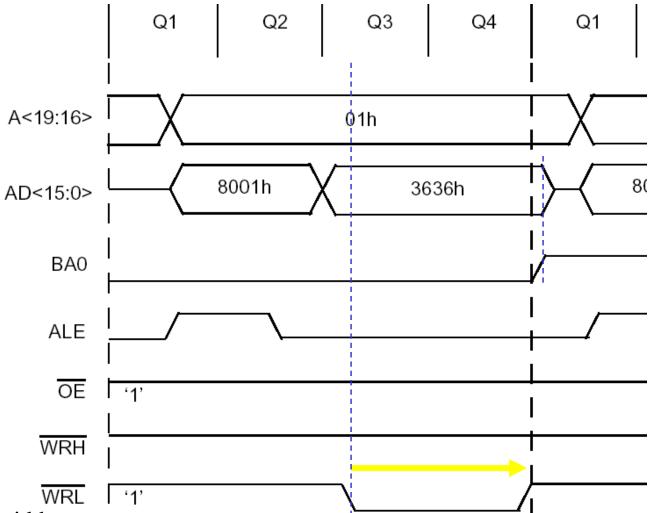

#### PUNTO DI VISTA DEL MICROPROCESSORE

Qualche dato: la massima frequenza di clock del bus esterno del micro è 25 MHz.

Quindi ogni ciclo di clock del bus esterno è pari a 1/25Mhz = 40 ns.

La durata di ogni Qi è pari a 40 ns.

Il micro genera gli indirizzi multiplexati a metà di Q1, dopo 20 ns dall'inizio del ciclo.

L'ALE si abbassa a metà di Q2, ovvero dopo 60 ns dall'inizio del ciclo.

A quel punto gli indirizzi vengono campionati dal latch 373 e, dopo un tempo di transito (che noi valuteremo nell'intorno di 10 ns) nel dispositivo, sono stabili alla porta ADDRESS della memoria.

Per quanto riguarda i cicli di lettura dati/opcode fetch, è fondamentale la forma d'onda del /CE e dell'/OE: il micro genera il /CE all'inizio di Q2, quindi dopo 40 ns dall'inizio del ciclo, e lo mantiene attivo fino a metà di Q1 del ciclo successivo, quindi 20 ns dopo la fine del ciclo di bus.

Questo per mantenere il data bus della memoria attivo anche dopo l'istante di campionamento dei dati da parte del micro (cosa che avviene alla fine di Q4 e che necessita della validità dei dati anche per qualche ns dopo la fine di Q4).

Il micro genera l'/OE all'inizio di Q3 e lo mantiene attivo fino alla fine di Q4, istante in cui avviene il campionamento del dato presente sul data bus.

Nel caso in cui ci fossero dei transceiver a valle della memoria per indirizzare correttamente il dato sul data bus alle porte del micro, si dovrà tenere conto anche di un ulteriore ritardo dall'istante di validità del dato alla porta della memoria all'istante di effettiva validità del dato alla porta del micro.

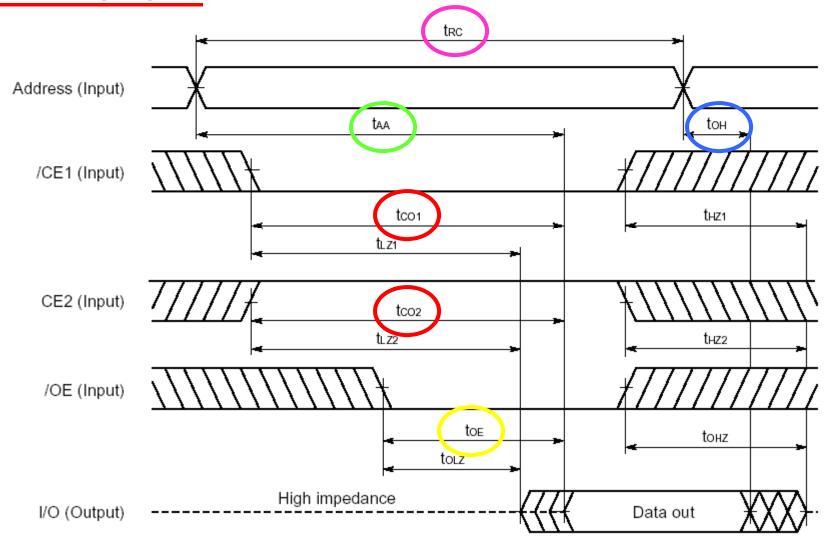

# Temporizzazioni nell'interfacciamento (memoria)

#### **READ CYCLE**

### Temporizzazioni nell'interfacciamento (memoria)

#### PUNTO DI VISTA DELLA MEMORIA

Il ciclo di lettura/scrittura è un evento asincrono se osservato dal punto di vista della memoria.

Il CLOCK di sistema e/o di bus non interviene in modo diretto sui pin della memoria in alcun modo.

Devono essere rispettati alcuni tempi minimi e massimi per l'interfacciamento corretto con la memoria, in caso contrario non si ha la certezza della corretta lettura/scrittura del dato stesso.

I tempi caratteristici delle memorie sono dichiarati sui data sheet e devono essere messi in relazione con il ciclo di bus del micro con cui si interfacciano.

In genere, si cerca di semplificare i calcoli di verifica delle temporizzazioni usando solo alcune temporizzazioni fondamentali:

**Tacc**: tempo minimo da cui devono essere attivi gli **indirizzi** ai pin del dispositivo (memoria) affinché il dispositivo risponda

TCE (o TCS): tempo minimo da cui deve essere attivo il Chip Enable (o Chip Select)

Per lettura:

TOE: tempo minimo da cui deve essere attivo il READ

Per scrittura:

**TWE**: tempo minimo da cui devono essere attivi il **WRITE** e i **DATI** (importante: insieme; chiaramente vincola il più lento dei due)

Non ci occupiamo dei tempi minimi per passare da High-Z a Low-Z per le linee dati delle memorie e in modo analogo non ci occupiamo dell'evento duale di passaggio da Low-Z ad High-Z alla fine del ciclo e dei suoi tempi massimi.

## Tempistiche fondamentali da data sheet NEC $\mu PD431000A$

| Parameter                        | Symbol | Vcc ≥ 4.5 V    |         |               |      | Vcc ≥ 3.0 V    |      | Unit |

|----------------------------------|--------|----------------|---------|---------------|------|----------------|------|------|

|                                  |        | μPD431         | 000A-70 | μPD431000A-85 |      | μPD431000A-A10 |      |      |

|                                  |        | μPD431000A-Axx |         |               |      |                |      |      |

|                                  |        | μPD431000A-Bxx |         |               |      |                |      |      |

|                                  |        | MIN.           | MAX.    | MIN.          | MAX. | MIN.           | MAX. |      |

| Read cycle time                  | trc    | 70             |         | 85            |      | 100            |      | ns   |

| Address access time              | taa    |                | 70      |               | 85   |                | 100  | ns   |

| /CE1 access time                 | tco1   |                | 70      |               | 85   |                | 100  | ns   |

| CE2 access time                  | tco2   |                | 70      |               | 85   |                | 100  | ns   |

| /OE to output valid              | toe    |                | 35      |               | 45   |                | 50   | ns   |

| Output hold from address change  | tон    | 10             |         | 10            |      | 10             |      | ns   |

| /CE1 to cutput in low impedance  | tLZ1   | 10             |         | 10            |      | 10             |      | iis  |

| CE2 to output in low impedance   | tızz   | 10             |         | 10            |      | 10             |      | ns   |

| /OE to output in low impedance   | toLz   | 4              |         | 5             |      | 5              |      | ns   |

| /CE1 to output in high impedance | tHZ1   |                | 25      |               | 30   |                | 35   | ns   |

| CE2 to output in high impedance  | tHZ2   |                | 25      |               | 30   |                | 35   | ns   |

| /O⊑ to output in high impedance  | tонz   |                | 25      |               | 30   |                | 35   | ns   |

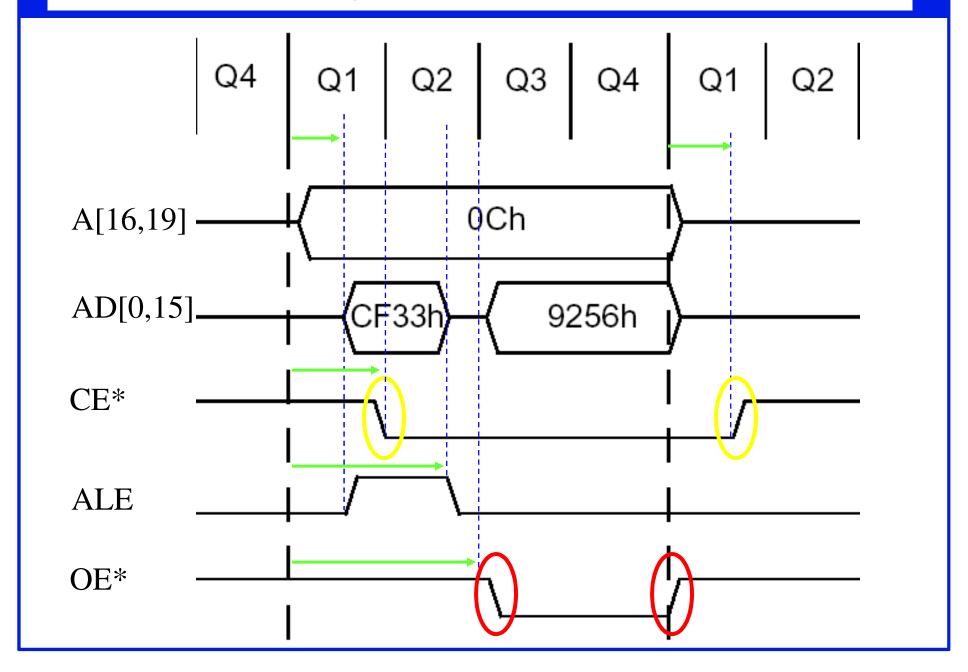

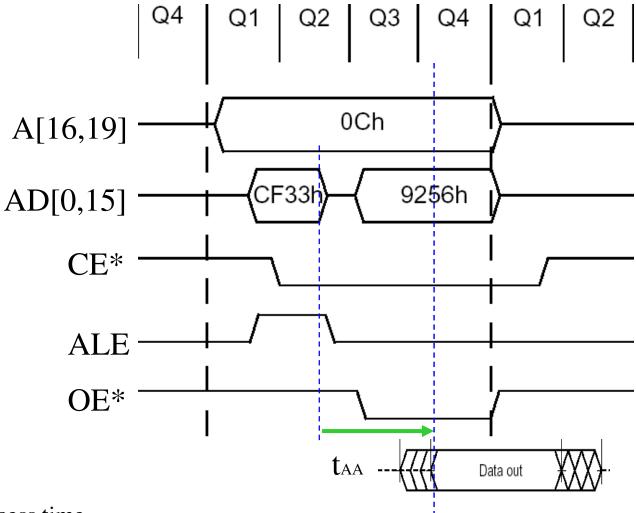

### Relazione tra le tempistiche (taa)

taa=access time

taa=70 ns per cui dalla metà di Q2 + 70 ns e si ha il dato valido dal punto di vista del tempo di accesso, quindi al max dopo 10 ns dall'inizio di Q4 i dati risulteranno validi sul data bus.

60 (t address valid da inizio ciclo) + 70 (taa) + 10 (t373) + 10 (t245) = 150 < 4\*Qi = 40\*4 = 160

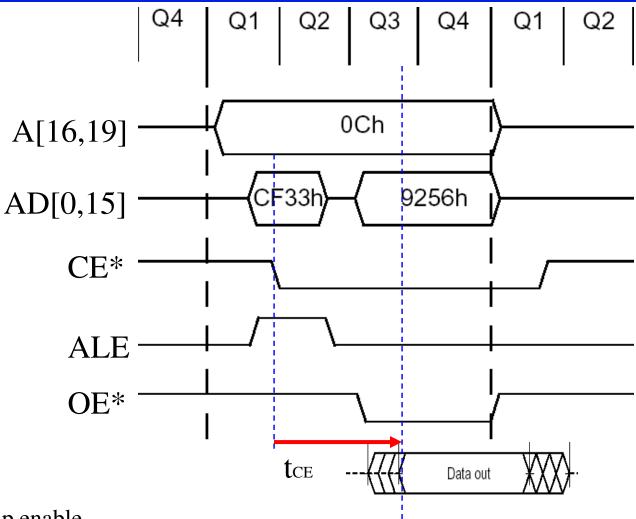

## Relazione tra le tempistiche (tce)

tce=chip enable

tce=70 ns per cui dalla fine di Q1 + 70 ns e si ha il dato valido dal punto di vista di /CE, quindi al max dopo 30 ns dall'inizio di Q3 i dati risulteranno validi sul data bus dal lato della memoria.

40 (t ce da inizio ciclo) + 70 (tce) + 10 (t245) = 120 < 4\*Qi = 40\*4 = 160

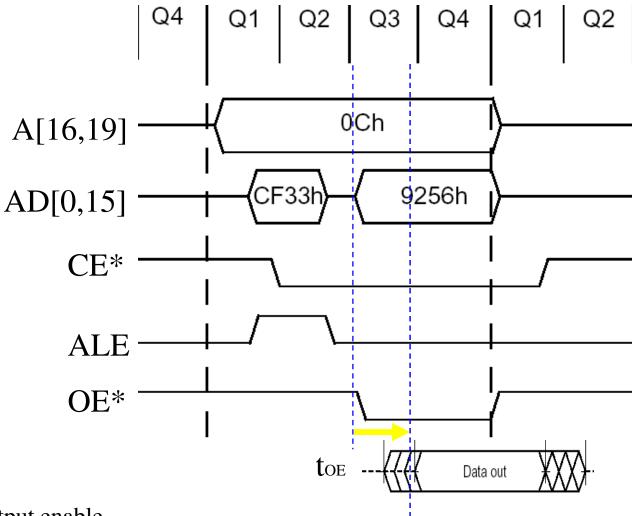

## Relazione tra le tempistiche (toe)

toe=output enable

toE=35 ns per cui dalla fine di Q2 + 35 ns e si ha il dato valido dal punto di vista del tempo di /OE, quindi al max dopo 35 ns dall'inizio di Q3 i dati risulteranno validi sul data bus.

80 (t oe da inizio ciclo) + 35 (toe) + 10 (t245) = 125 < 4\*Qi = 40\*4 = 160

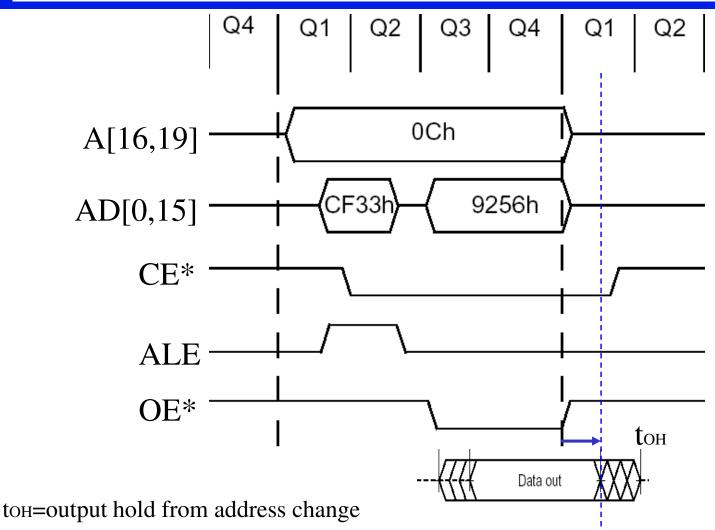

### Relazione tra le tempistiche (toн)

toH=15 ns al minimo, per cui dalla fine di Q4 + 10 ns si ha ancora il dato valido e quindi il campionamento del micro può avvenire alla fine di Q4 ed avere quel minimo di ns necessari all'effettiva acquisizione del dato dal bus.

160 (t oh da inizio ciclo) + 10 (toh) = 170 > 4\*Qi = 40\*4 = 160

## Relazione tra le tempistiche (trc)

trc=read cycle

trc=70 ns al minimo, per cui dalla metà di Q2 + 70 ns si devono ancora avere gli indirizzi validi e quindi il campionamento del micro può avvenire alla fine di Q4 ed avere quel minimo di ns necessari all'effettiva acquisizione del dato dal bus.

60 (t rc da inizio ciclo) + 70 (trc) + 10 (t373) = 140 < 4\*Qi = 40\*4 = 160

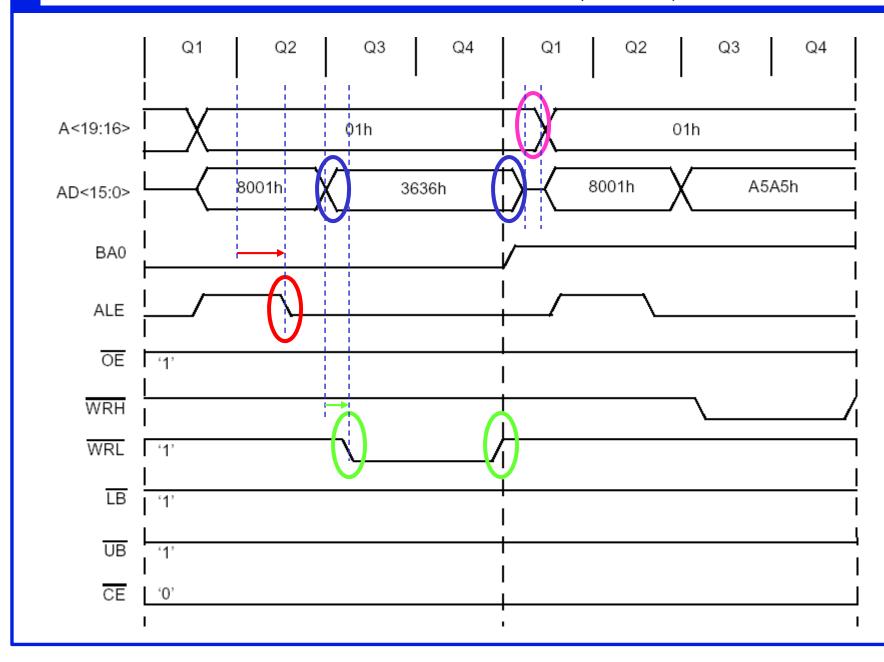

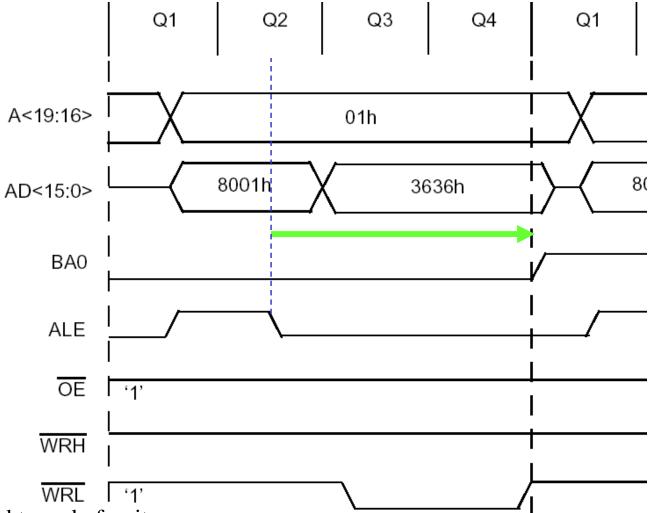

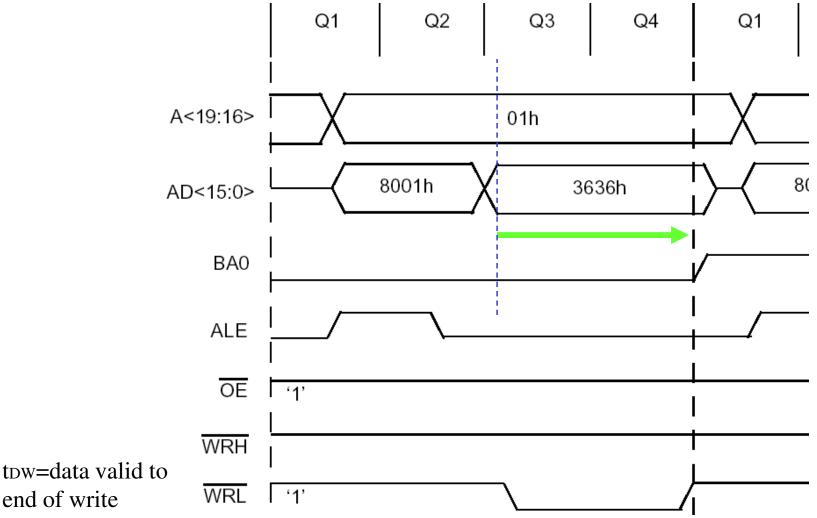

## Ciclo di Data Write (micro)

#### Temporizzazioni nell'interfacciamento in scrittura (micro)

#### PUNTO DI VISTA DEL MICROPROCESSORE

Qualche dato: la massima frequenza di clock del bus esterno del micro è 25 MHz.

Quindi ogni ciclo di clock del bus esterno è pari a 1/25Mhz = 40 ns.

La durata di ogni Qi è pari a 40 ns.

Il micro genera gli indirizzi multiplexati a metà di Q1, dopo 20 ns dall'inizio del ciclo.

L'ALE si abbassa a metà di Q2, ovvero dopo 60 ns dall'inizio del ciclo.

A quel punto gli indirizzi vengono campionati dal latch 373 e, dopo un tempo di transito (che noi valuteremo nell'intorno di 10 ns) nel dispositivo, sono stabili alla porta ADDRESS della memoria.

Per quanto riguarda i cicli di scrittura dati, è fondamentale la forma d'onda del /CE e dell'/WR: il micro genera il /CE all'inizio di Q2, quindi dopo 40 ns dall'inizio del ciclo, e lo mantiene attivo fino a metà di Q1 del ciclo successivo, quindi 20 ns dopo la fine del ciclo di bus.

Questo per mantenere il data bus della memoria attivo anche dopo l'istante di campionamento dei dati da parte del micro (cosa che avviene alla fine di Q4 e che necessita della validità dei dati anche per qualche ns dopo la fine di Q4).

Il micro genera il /WR dopo 5 ns (circa, il dato è ricavato dalle forme d'onda ma non è presente nei data sheet!) dall'inizio di Q3 e lo mantiene attivo fino alla fine di Q4, istante in cui avviene il campionamento del dato presente sul data bus.

Nel caso in cui ci fossero dei transceiver a valle del micro per indirizzare correttamente il dato sul data bus alle porte della memoria, si dovrà tenere conto anche di un ulteriore ritardo dall'istante di validità del dato alla porta del micro all'istante di effettiva validità del dato alla porta della memoria.

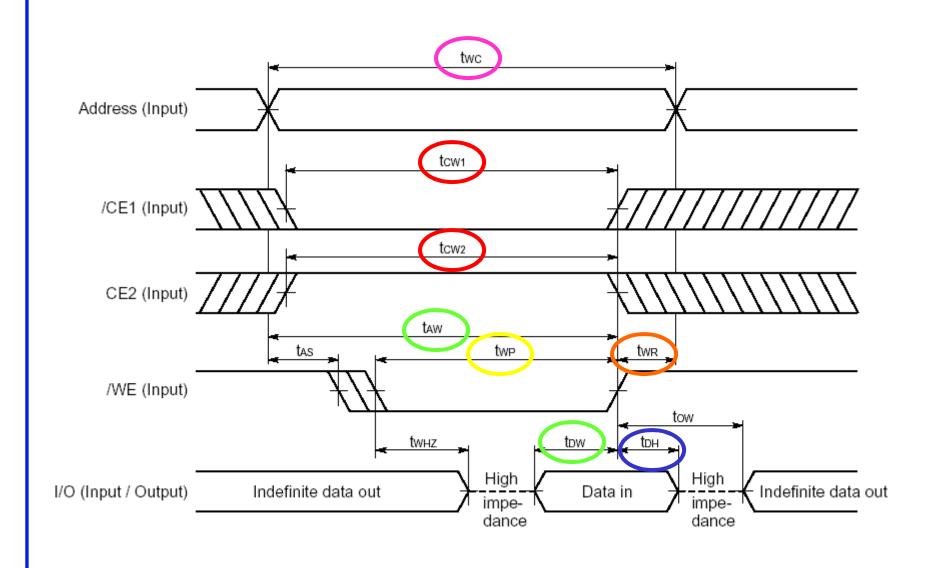

## Ciclo di Data Write (memoria)

## Tempistiche fondamentali da data sheet NEC $\mu PD431000A$

| Parameter                       | Symbol | Vcc ≥ 4.5 V    |         |               |      | Vcc ≥ 3.0 V    |      | Unit |

|---------------------------------|--------|----------------|---------|---------------|------|----------------|------|------|

| •                               |        | μPD431         | 000A-70 | μPD431000A-85 |      | μPD431000A-A10 |      |      |

|                                 |        | μPD431000A-Axx |         |               |      |                |      |      |

|                                 |        | μPD431000A-Bxx |         |               |      |                |      |      |

|                                 |        | MIN.           | MAX.    | MIN.          | MAX. | MIN.           | MAX. |      |

| Write cycle time                | twc    | 70             |         | 85            |      | 100            |      | ns   |

| /CE1 to end of write            | tcw1   | 55             |         | 70            |      | 80             |      | ns   |

| CE2 to end of write             | tcw2   | 55             |         | 70            |      | 80             |      | ns   |

| Address valid to end of write   | taw    | 55             |         | 70            |      | 80             |      | ns   |

| Address setup time              | tas    | 0              |         | 0             |      | 0              |      | ns   |

| Write pulse width               | twp    | 50             |         | 60            |      | 60             |      | ns   |

| Write recovery time             | twr    | 5              |         | 5             |      | 0              |      | ns   |

| Data valid to end of write      | tow    | 35             |         | 35            |      | 60             |      | ns   |

| Data hold time                  | tон    | 0              |         | 0             |      | 0              |      | ns   |

| /WE to output in high impedance | twнz   |                | 25      |               | 30   |                | 35   | ns   |

| Output active from end of write | tow    | 5              |         | 5             |      | 5              |      | ns   |

### Relazione tra le tempistiche (taw)

taw=address valid to end of write

taw=55 ns al minimo, per cui dalla metà di Q2 + 55 ns si devono ancora avere gli indirizzi validi come tempo minimo perché campionamento della memoria sia valido.

$$60 \text{ (t ale da inizio ciclo)} + 55 \text{ (taw)} + 10 \text{ (t373)} = 125 < 4*Qi = 40*4 = 160$$

### Relazione tra le tempistiche (twc)

twc=write cycle

twc=70 ns al minimo, per cui dalla metà di Q2 + 70 ns si devono ancora avere gli indirizzi validi alle porte della memoria come tempo minimo perché campionamento della memoria sia valido.

$$60 \text{ (t ale da inizio ciclo)} + 70 \text{ (twc)} + 10 \text{ (t373)} = 140 < 4*Qi + 5 = 40*4 + 5 = 165$$

## Relazione tra le tempistiche (twp)

twp=write pulse width

twp=50 ns al minimo, per cui da 10 ns dopo l'iizio di Q3 + 50 ns deve essere minore o uguale alla lunghezza del ciclo di bus.

90 (t da inizio ciclo) + 50 (twp) = 140 < 4\*Qi = 40\*4 = 160

#### Relazione tra le tempistiche (tcw)

tcw=chip enable to end of write

tcw=55 ns al minimo, per cui la durata dell'intervallo di tempo che va dall'inizio di Q1 all'inizio di Q2 + 55 ns dev'essere minore della lunghezza del ciclo di bus perché campionamento della memoria sia valido.

40 (t da inizio ciclo) + 55 (tcw) = 95 < 4\*Qi = 40\*4 = 160

### Relazione tra le tempistiche (tow)

tDW=35 ns al minimo, per cui da 5 ns dopo l'inizio di Q3 alla fine del write si devono ancora avere i dati validi alle porte della memoria per almeno 35 ns come tempo minimo perché campionamento della memoria sia valido (nell'eventualità di presenza dei 245 si calcolino 10 ns di ritardo.

85 (tdw da inizio ciclo) + 35 (tdw) + 10 (t245) = 130 < 4\*Qi = 40\*4 = 160