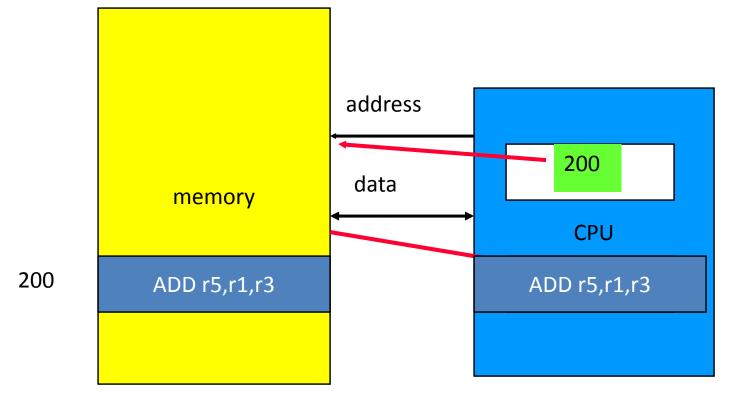

#### CPU + memory

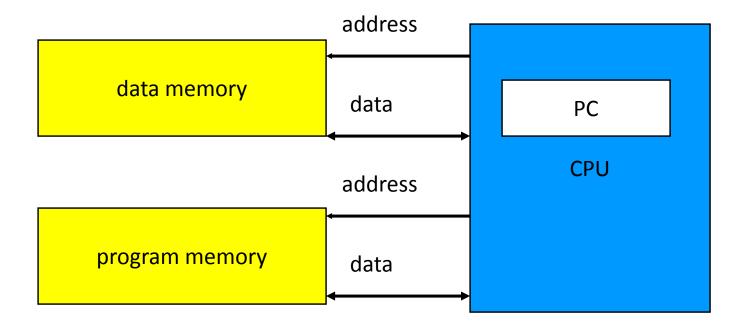

#### Harvard architecture

#### RISC vs. CISC

- Complex instruction set computer (CISC):

- many addressing modes;

- many operations.

- Reduced instruction set computer (RISC):

- load/store;

- pipelinable instructions.

#### Instruction set characteristics

- Fixed vs. variable length.

- Addressing modes.

- Number of operands.

- Types of operands.

#### Programming model

- Programming model: registers visible to the programmer.

- Some registers are not visible (IR).

# Multiple implementations

- Successful architectures have several implementations:

- varying clock speeds;

- different bus widths;

- different cache sizes;

- etc.

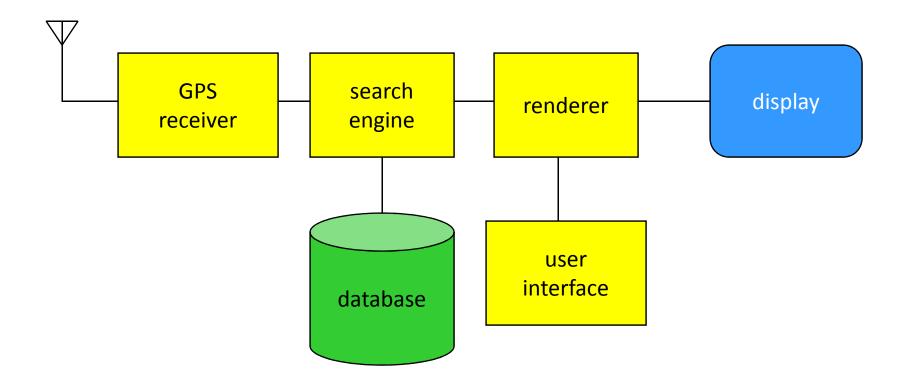

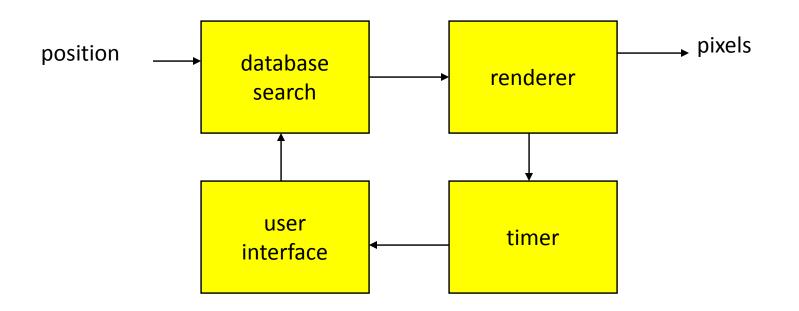

# GPS moving map block diagram

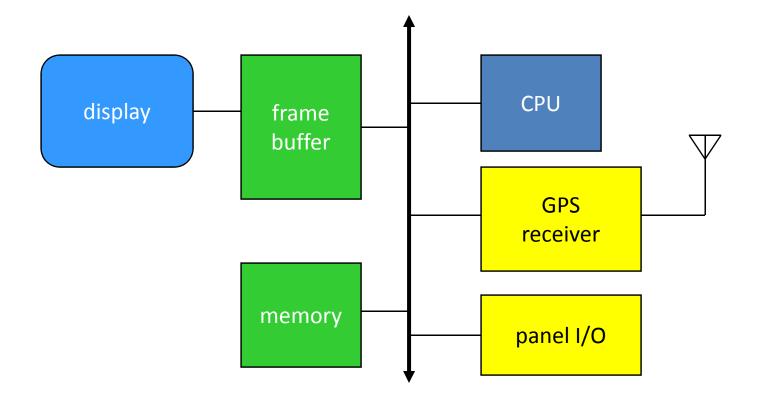

# GPS moving map hardware architecture

# GPS moving map software architecture

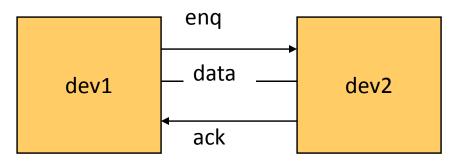

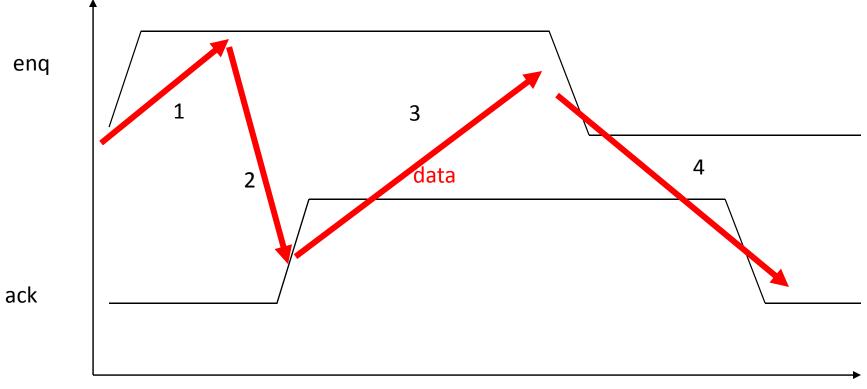

### Four-cycle handshake

- Basis of many bus protocols.

- Uses two wires:

- enq (enquiry);

- ack (acknowledgment).

#### Four-cycle example

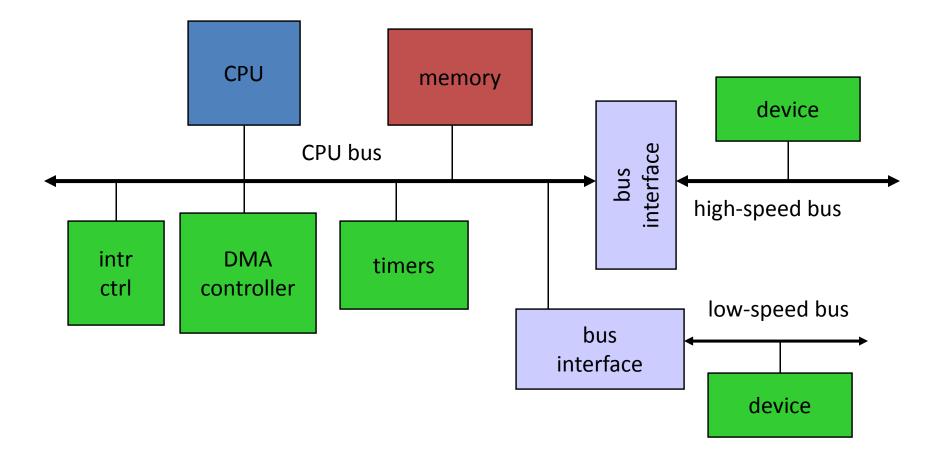

# Typical bus signals

- Clock.

- R/W': true when bus is reading.

- Address: a-bit bundle.

- Data: n-bit bundle.

- Data ready'.

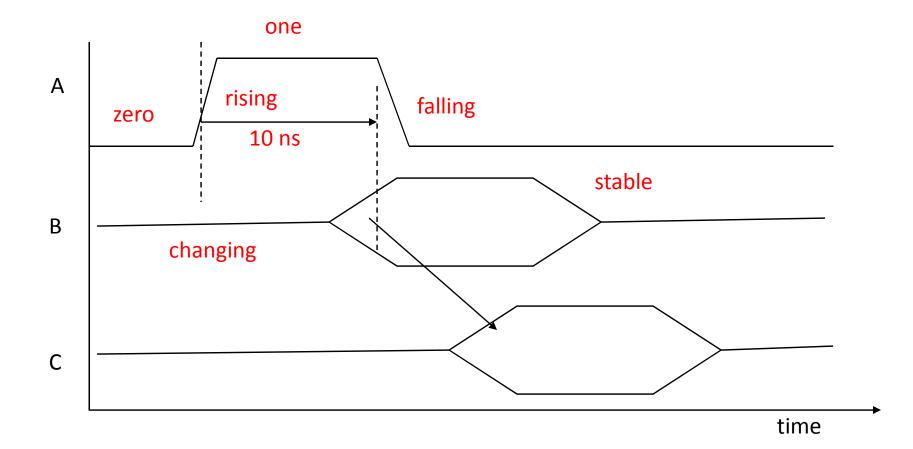

### Timing diagrams

# Typical bus timing for read

- CPU:

- asserts address, address enable;

- set R/W'=1.

- Memory:

- asserts data;

- asserts data ready'.

- CPU:

- De-asserts address, address enable.

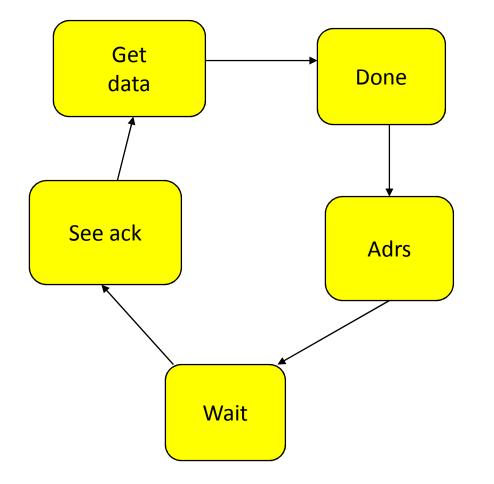

#### Bus read state diagram

#### Transaction types

- Wait state:

- state in a bus transaction to wait for acknowledgment.

- Disconnected transfer:

- bus is freed during wait state.

- Burst:

- multiple transfers.

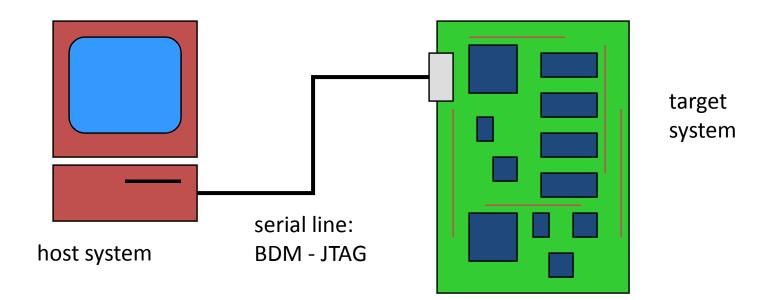

Host/target design: Cross-Compilazione

Use a host system to prepare software for target system:

### Typical PC hardware platform

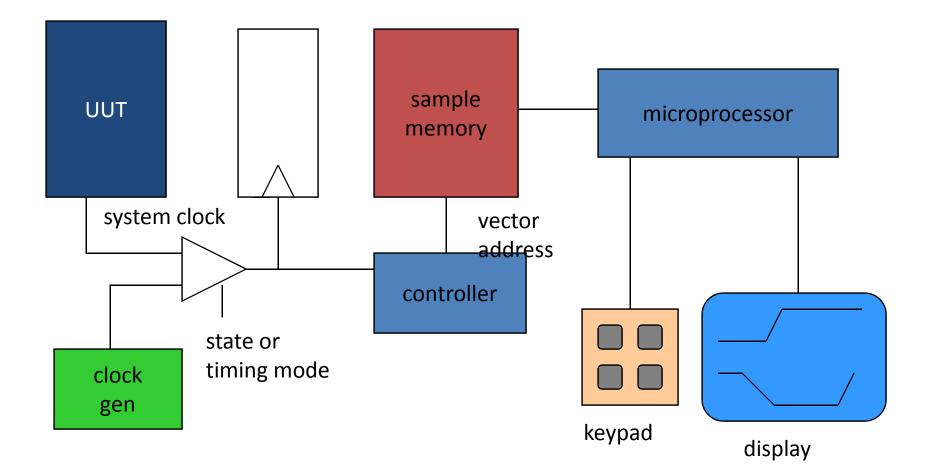

#### Logic analyzers

• A logic analyzer is an array of low-grade oscilloscopes:

#### Logic analyzer architecture

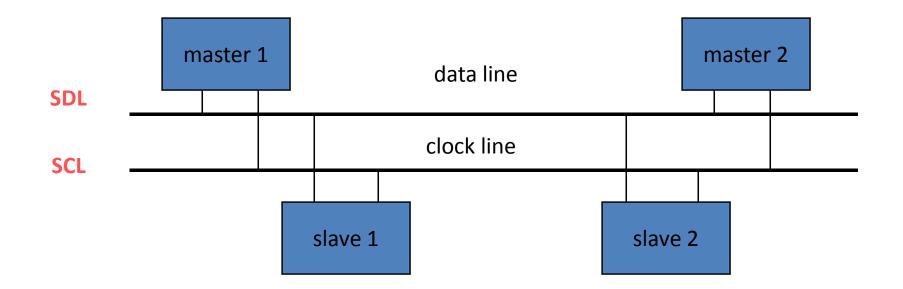

# I<sup>2</sup>C bus

- Designed for low-cost, medium data rate applications.

- Characteristics:

- serial;

- multiple-master;

- fixed-priority arbitration.

- Several microcontrollers come with built-in I<sup>2</sup>C controllers.

# I<sup>2</sup>C physical layer

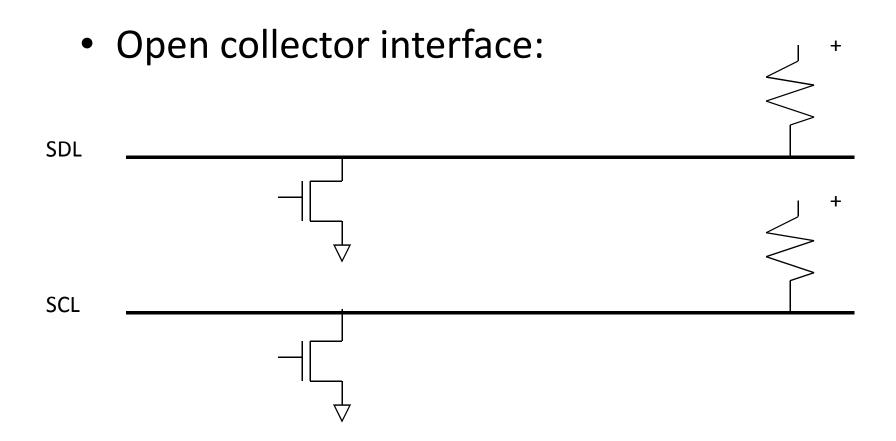

#### I<sup>2</sup>C electrical interface

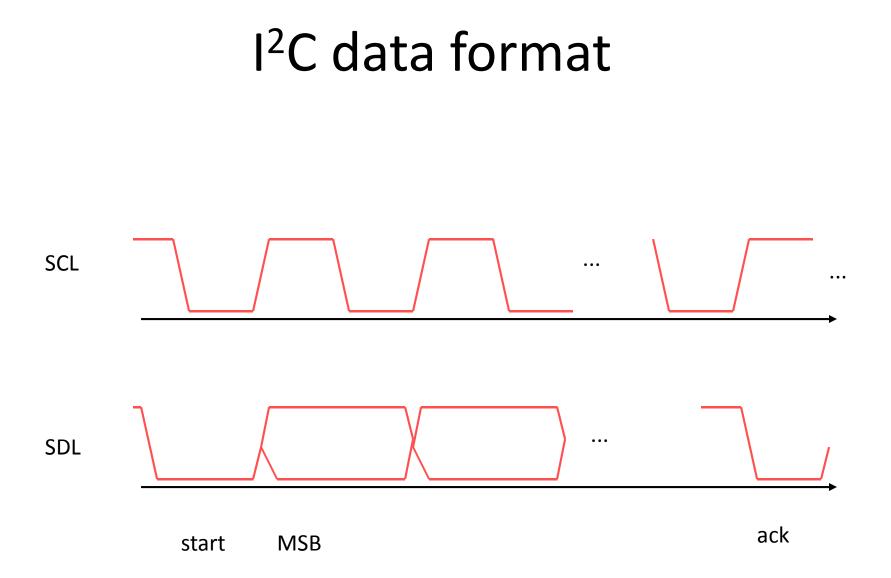

# I<sup>2</sup>C signaling

- Sender pulls down bus for 0.

- Sender listens to bus---if it tried to send a 1 and heard a 0, someone else is simultaneously transmitting.

- Transmissions occur in 8-bit bytes.

# I<sup>2</sup>C data link layer

- Every device has an address (7 bits in standard, 10 bits in extension).

- Bit 8 of address signals read or write.

- General call address allows broadcast.

## I<sup>2</sup>C bus arbitration

- Sender listens while sending address.

- When sender hears a conflict, if its address is higher, it stops signaling.

- Low-priority senders relinquish control early enough in clock cycle to allow bit to be transmitted reliably.

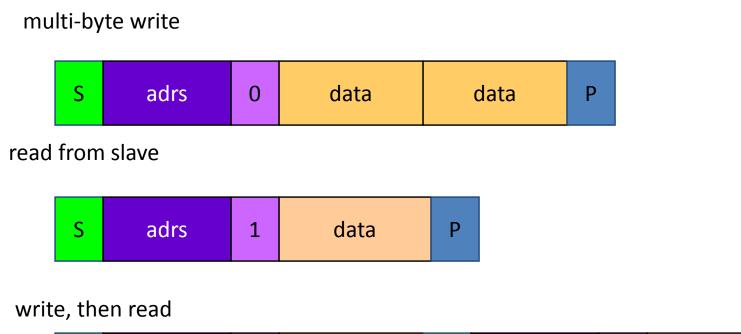

# I<sup>2</sup>C transmissions

| S | adrs | 0 | data | S | adrs | 1 | data | Р |

|---|------|---|------|---|------|---|------|---|

|---|------|---|------|---|------|---|------|---|

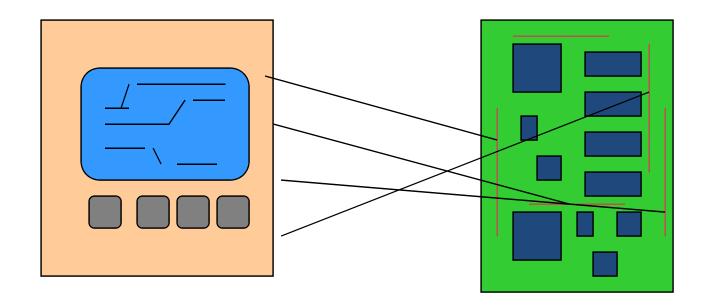

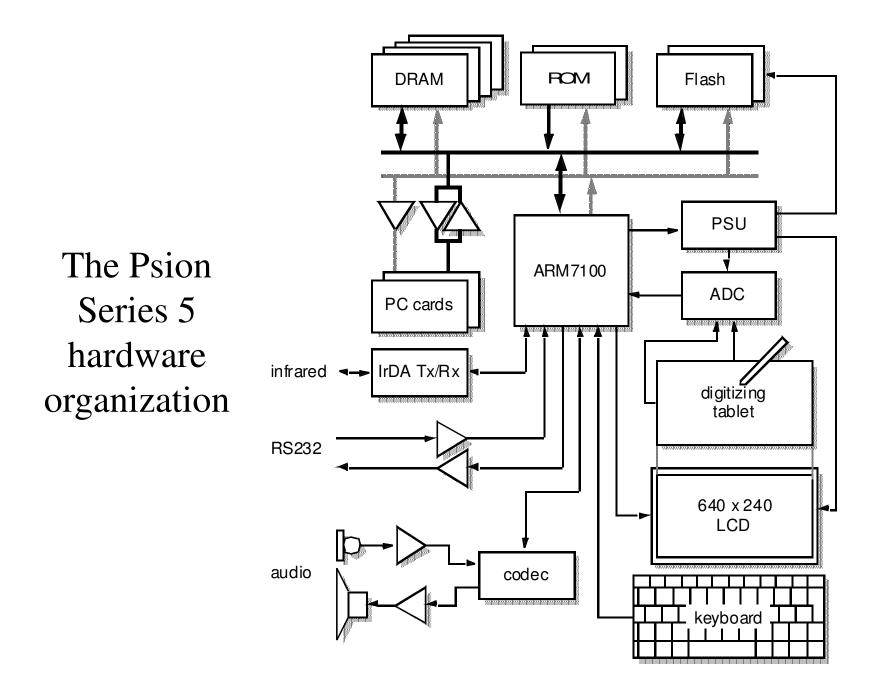

# Personal digital assistant

- PDA: portable, specialized information device.

- Characteristics:

- low cost for consumer market;

- physically small;

- battery-powered;

- software-rich.

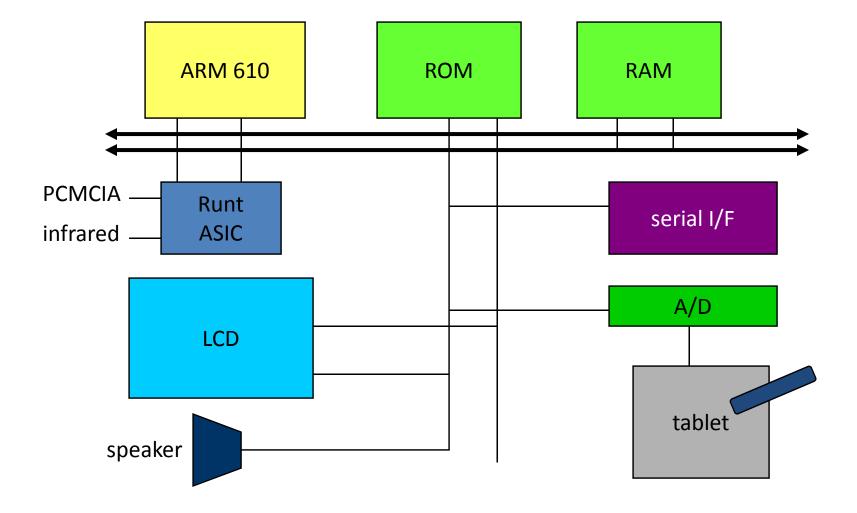

#### **Apple Newton**

- First modern PDA.

- Original used ARM 610; later version used StrongARM (ARM7) last: ARM9.

- Support operations in Runt ASIC: DMA, realtime clock, video interface, audio, PCMCIA.

- Software written in NewtonScript language.

#### Newton hardware architecture

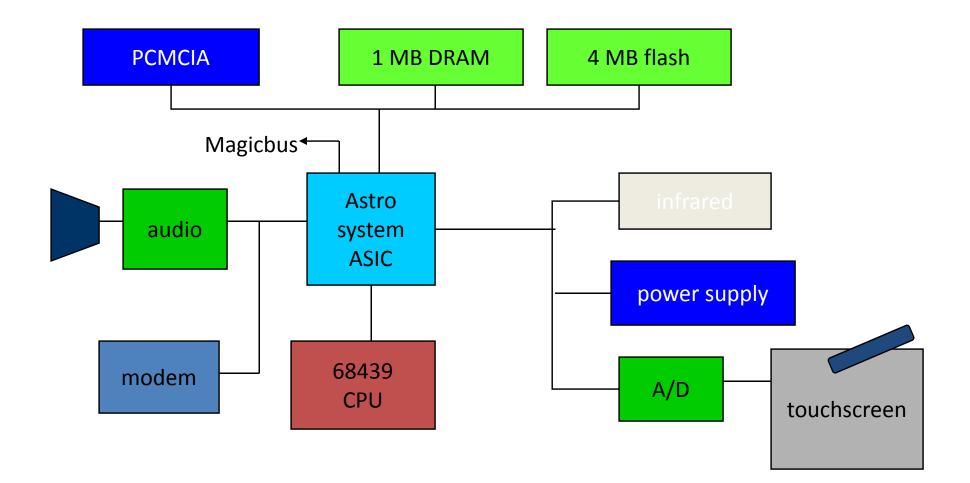

# Motorola Envoy hardware architecture

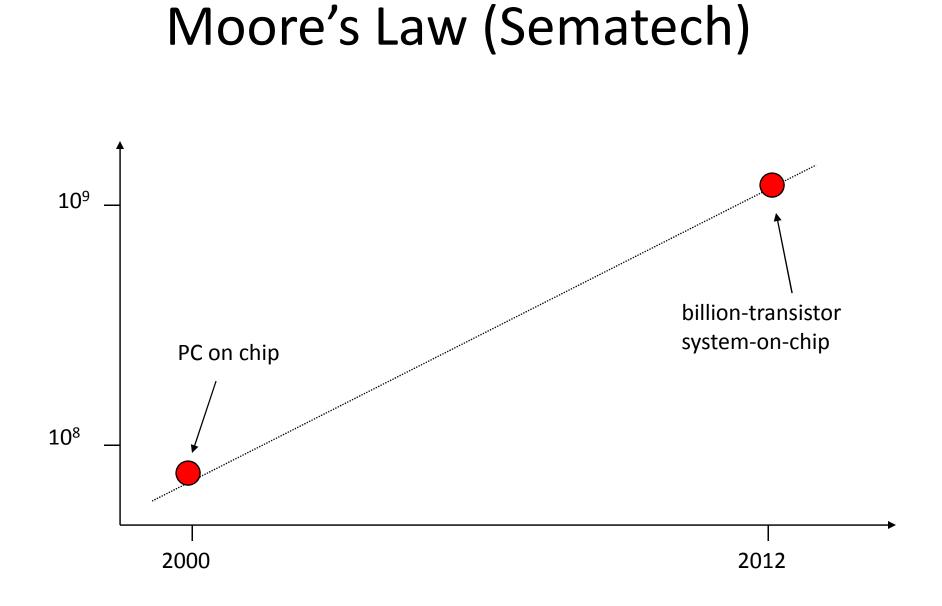

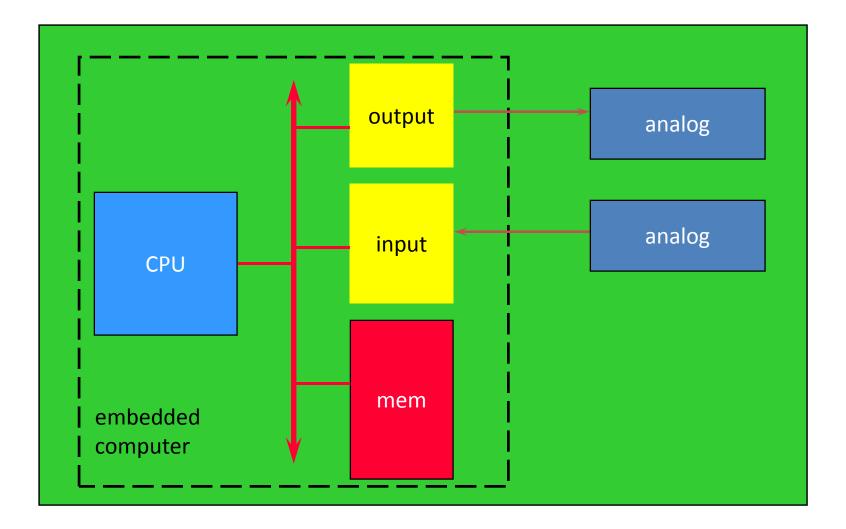

#### Embedding a computer

# Examples

- Personal digital assistant (PDA).

- Printer.

- Cell phone.

- Automobile: engine, brakes, dash, etc.

- Television.

- Household appliances.

- PC keyboard (scans keys).

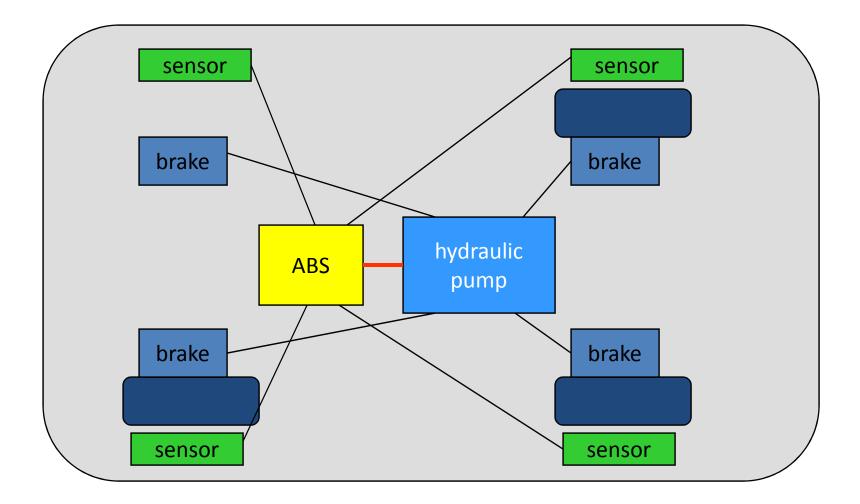

# BMW 850i brake and stability control system

- Anti-lock brake system (ABS): pumps brakes to reduce skidding.

- Automatic stability control (ASC+T): controls engine to improve stability.

- ABS and ASC+T communicate.

- ABS was introduced first---needed to interface to existing ABS module.

#### BMW 850i, cont'd.

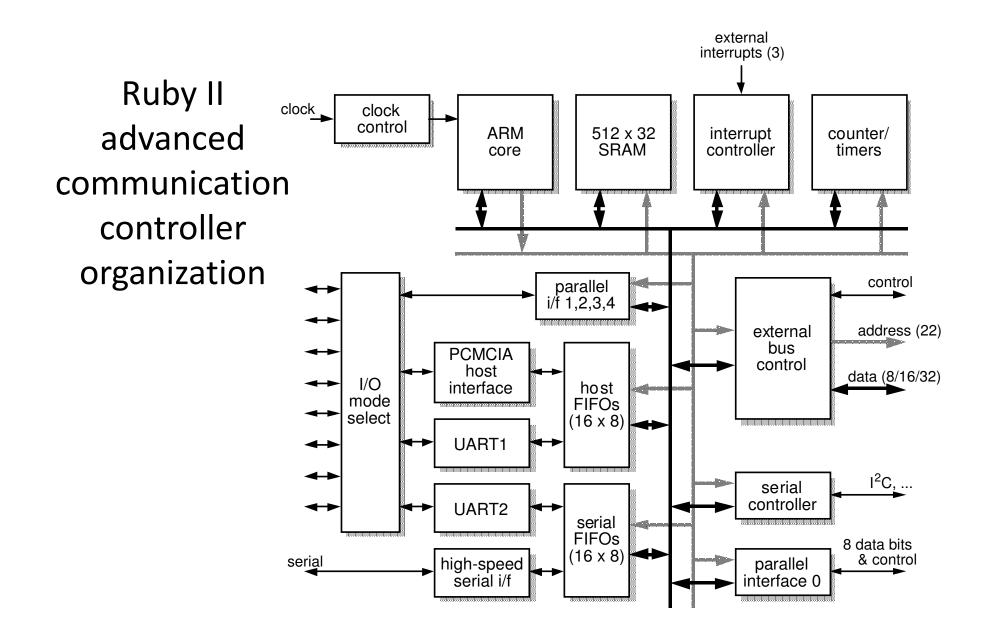

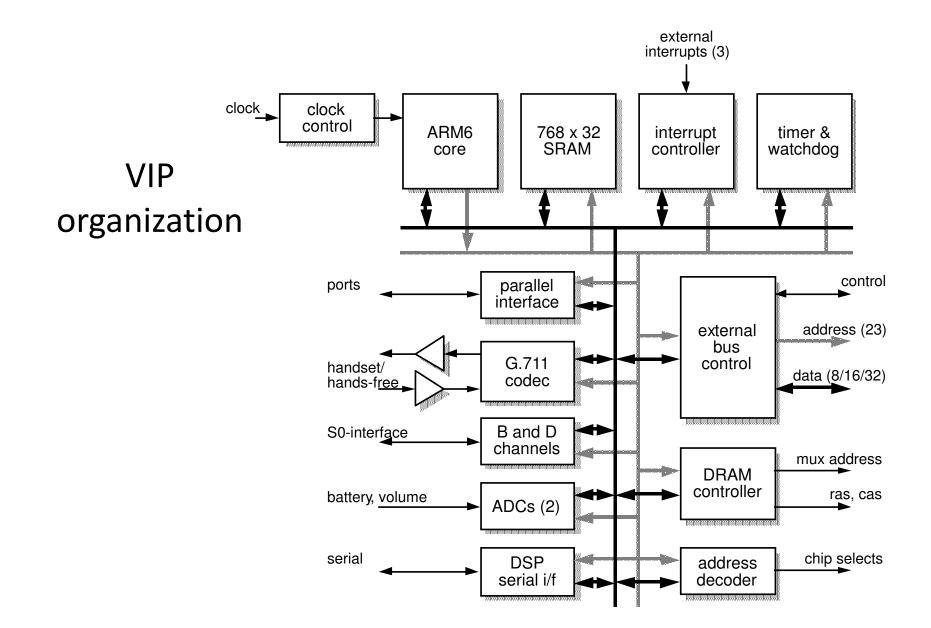

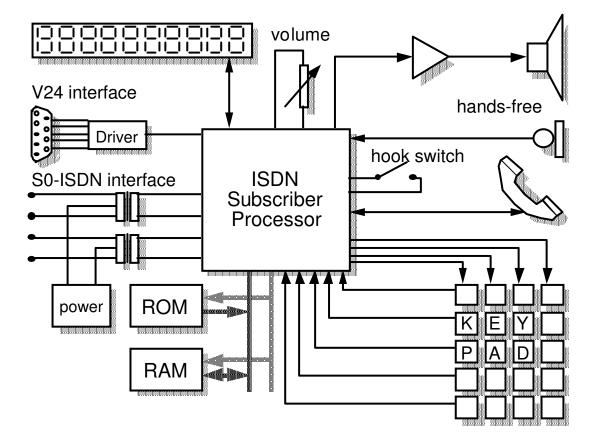

# **Typical VIP system configuration**

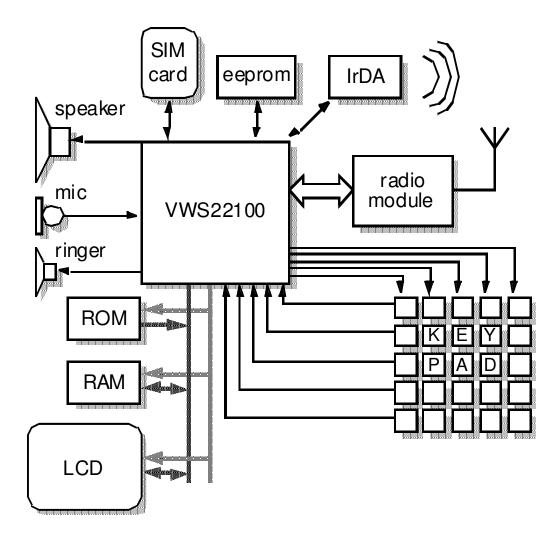

#### OneC VWS22100 GSM chip organization

#### Typical GSM handset architecture

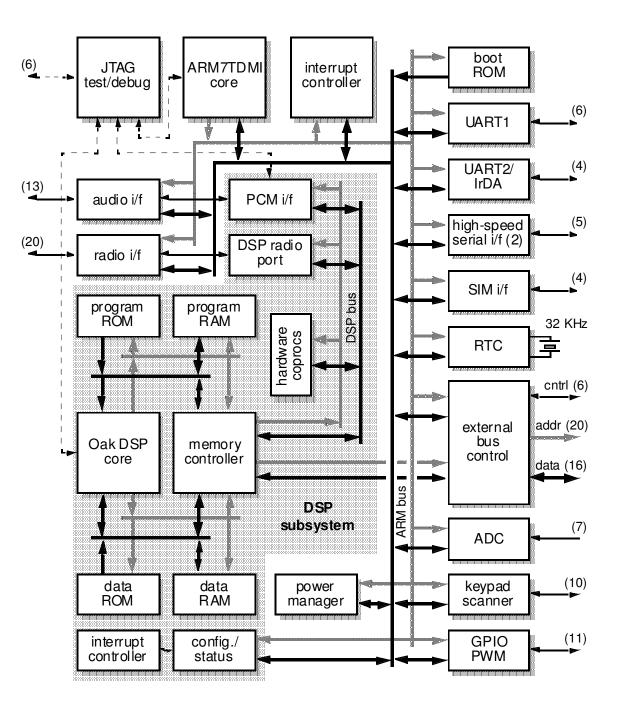

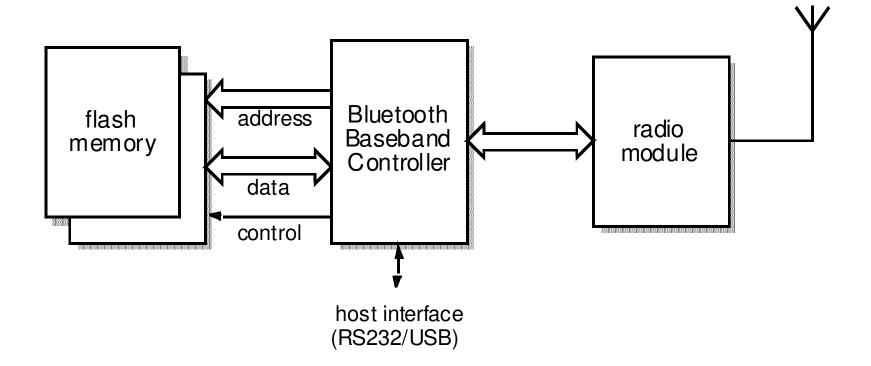

#### Ericsson-VLSI Bluetooth Baseband Controller organization

### **Typical Bluetooth application**

# **Bluetooth characteristics**

| Process      | 0.25 um | Transistors | 4,300,000         | MIPS   | 12    |

|--------------|---------|-------------|-------------------|--------|-------|

| Metal layers | 3       | Die area    | $20 \text{ mm}^2$ | Power  | 75 mW |

| Vdd          | 2.5 V   | Clock       | 0 – 13 MHz        | MIPS/W | 160   |

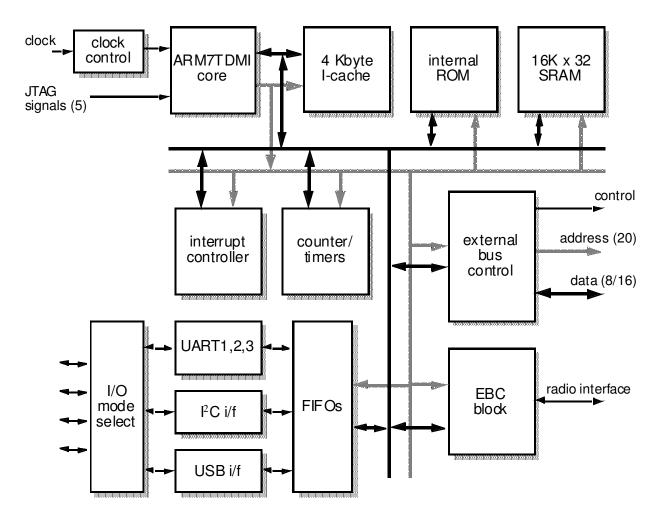

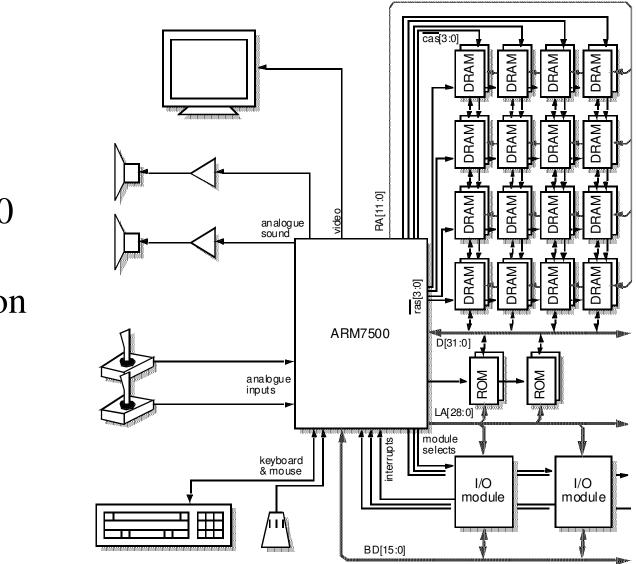

Typical ARM7500 system organization

# ARM7500 characteristics

| Process      | 0.6 um | Transistors | 550,000           |        | 30     |

|--------------|--------|-------------|-------------------|--------|--------|

| Metal layers | 2      | Die area    | $70 \text{ mm}^2$ | Power  | 690 mW |

| Vdd          | 5 V    | Clock       | 0 to 33 MHz       | MIPS/W | 43     |

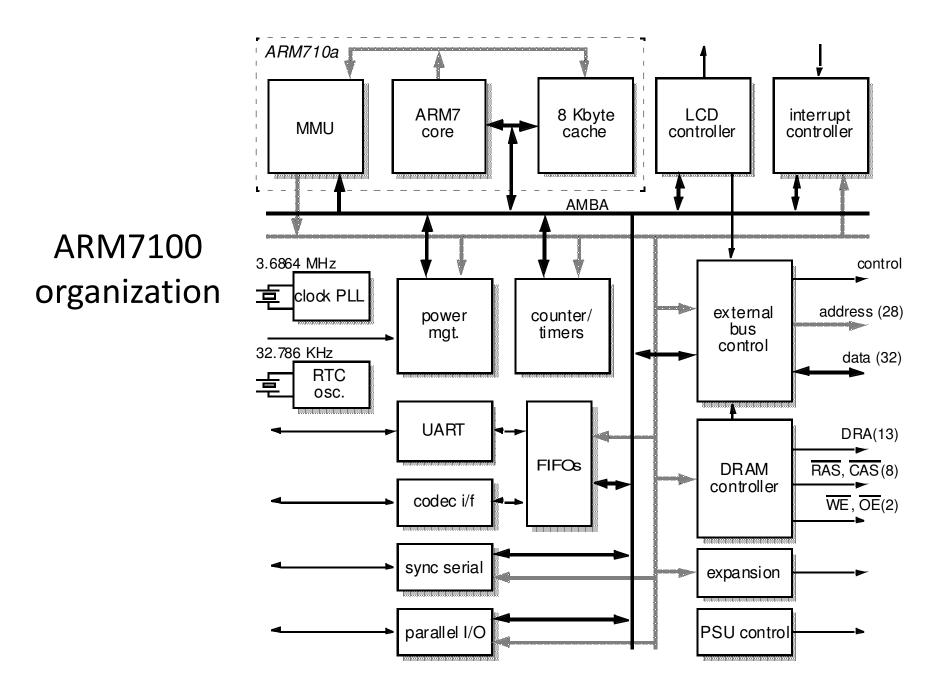

#### ARM7100 characteristics

Process Metal layers Vdd 0.6 um **Transistors** 2 **Die area** 3.3 V **Clock**

| N/A        | MIPS   | 30    |

|------------|--------|-------|

| N/A $mm^2$ | Power  | 14 mW |

| 18.432 MHz | MIPS/W | 212   |

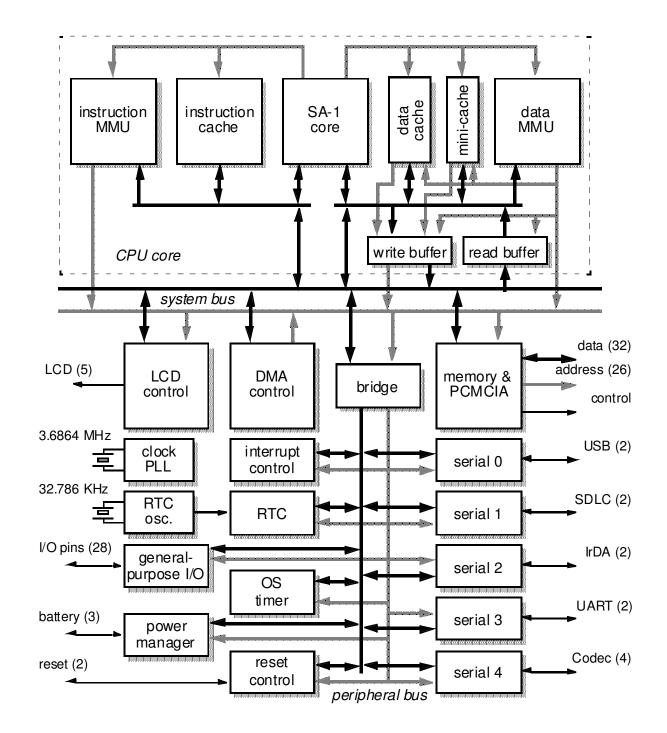

SA-1100 organization

#### SA-1100 characteristics

Process Metal layers Vdd 0.35 um **Transistors** 3 **Die area** 1.5/2 V **Clock**  2,500,000<br/>75 mm²MIPS<br/>Power220/250<br/>330/550 mW190/220 MHzMIPS/W665/450