# Guasti di tipo bridging

#### M. Favalli

Engineering Department in Ferrara

#### Difetti

Un bridging é dato dalla presenza di cammini conduttivi fra nodi del circuito che dovrebbero essere isolati

- Impuritá

- Disallineamento fra le maschere di layout

- Elettromigrazione

- Mancanza di materiale isolante

#### **Sommario**

- Difetti

- Classificazione

- Effetti e metodi di collaudo

- Modelli

### Classificazione

- Topologia

- numero di nodi coinvolti: tipicamente 2

- posizione dei nodi coinvolti: interni (intra cell), esterni (inter cell)

- topologia della rete affetta dal guasto: feedback, non-feedback

- Parametri

- corto circuito (shorts)

- bridging di tipo resistivo

#### Nota

Qui considereremo principalmente guasti esterni fra uscite di gate (ad esempio non si considerano guasti che coinvolgono elementi di memoria)

#### Guasti interni/esterni

- Interni: fra due nodi dello stesso gate

- Esterni: fra le uscite di due gate

- Possibilitá di bridging fra nodi interni di gate diversi

- Maggiore probabilitá dei guasti esterni

- I guasti da considerare sono individuati da algorimi che ricevono il layout del circuito in ingresso

# Effetti dei bridging

- Comportamento statico del circuito: errori logici

- Assorbimento di corrente statica: CMOS e FinFET

- Cambiamento delle prestazioni dinamiche (ritardi)

- A ognuno di questi effetti corrisponde una tecnica per rivelare la presenza del guasto

- collaudo funzionale

- *I<sub>DDO</sub>* testing

- delay fault testing o at-speed testing

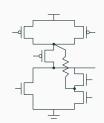

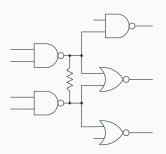

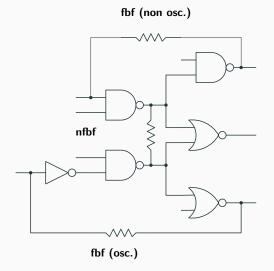

#### Retroazione

- Un bridging che (non)

costruisce una retroazione si

dice (non) feedback bridging

fault

- La presenza di retroazione puó dare luogo a memorizzazione o oscillazioni dipendentemente dalla paritá nel numero di inversioni nel cammino logico fra i due nodi interessati al guasto

## **Parametri**

- Topologia delle reti di transistori delle celle direttamente coinvolte e di quelle nel loro fan-out

- Parametri elettrici (dimensionamento) dei transistori di tali reti

- Tensione di alimentazione

- Temporizzazioni del circuito (ritardi e freguenza di clock)

- Resistenza del bridging

#### Condizioni di attivazione

- I due nodi cortocircuitati devono essere controllati a valori logici diversi nel circuito privo di guasti

- Nel circuito guasto tali nodi si trovano quindi su un cammino conduttivo fra l'alimentazione e la massa

- Le tensioni di uscita dei gate coinvolti si portano a valori intermedi fra massa e alimentazione e dipendono da

- tipo di logica (CMOS, FinFET)

- parametri circuitali

- dagli ingressi del o dei gate coinvolti

- Considereremo il caso dei bridging esterni (nfbf)

### Propagazione degli effetti del guasto

#### Condizioni necessarie

- Logiche: almeno uno dei due segnali deve essere osservabile in uscita

- Elettriche: il segnale osservabile deve dare luogo a un errore logico

- almeno uno dei gate attraverso cui si propaga tale segnale deve interpretare il suo valore di tensione intermedio come un errore logico

- quindi il valore da propagare é quello che perde il conflitto di conduttanze

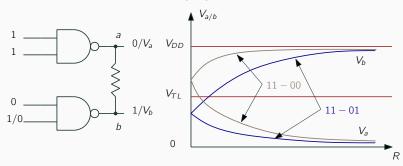

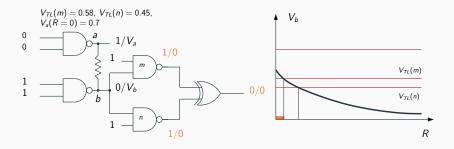

#### Valori di tensione

In circuiti CMOS, fissate le reti dei gate coinvolti e i parametri circuitali, i valori di tensione intermedi dei nodi coinvolti dipendono dal test e dalla resistenza R del bridging

### Esempio

## **Esempio**

## Propagazione degli effetti del guasto

Le condizioni di propagazione degli effetti del guasto sono in realtá molto piú complesse rispetto all'esempio

- La soglia logica non é  $V_{DD}/2$  ma dipende da:

- tipo di gate

- ingresso (potrebbero anche esserci piú ingressi a valori di tensione intermedi)

- valori logici agli altri ingressi del gate (AOI, OAI)

- La soglia logica é soggetta a significative variazioni statistiche nello stesso chip e da chip a chip

- I gate nel fan-out dei segnali affetti dal bridging

- possono interpretare in maniera diversa lo stesso valore di tensione

- hanno un guadagno finito, per cui non normalizzano immediatamente a 0 e 1 le tensioni intermedie

### **Esempio**

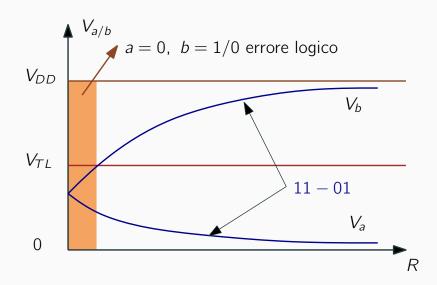

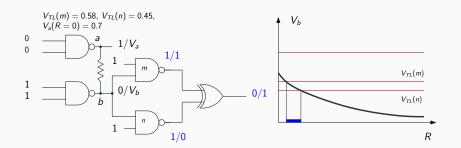

- Quale dei due test é meglio?

- Decide l'intervallo di resistenze

- Se applico 11-00, ci sono dei valori di *R* che non danno luogo a errore, ma che lo danno applicando 11-01

- Quindi 11-01 é un test migliore perché copre piú casi

# Esempi di propagazione degli effetti di bridging

- Vedremo una serie di esempi in cui si approssima al livello logico il comportamento di un bridging in un circuito CMOS in condizioni nominali

- nel primo esempio si tiene conto solo del conflitto di conduttanze supponendo che tutti i gate nel fan-out abbiano soglia pari a  $V_{DD}/2$

- nel secondo si mostra come le soglie diverse di questi gate possano invalidare alcuni test

- Questi esempi ci aiutano a capire alcuni problemi tipici di questo tipo di guasti e i relativi modelli

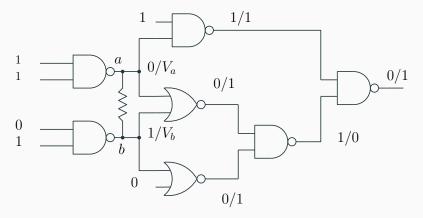

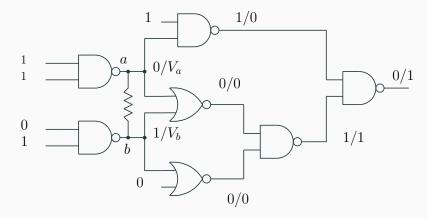

## Esempio - soglie a $V_{DD}/2$

Test che rivela il guasto se prevale il valore basso ( $V_a < V_{DD}/2$ ,  $V_b < V_{DD}/2$ )

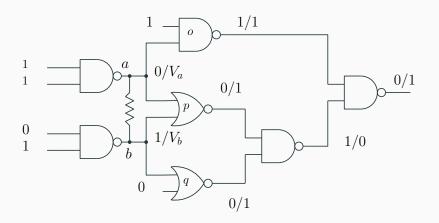

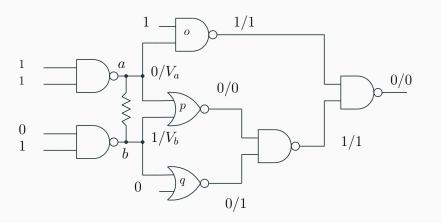

# Esempio - soglie nominali

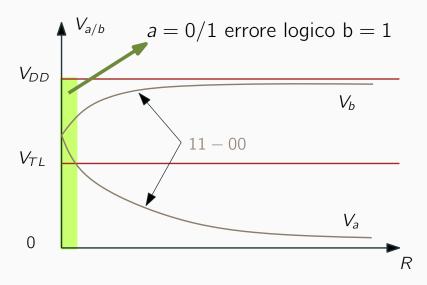

Il test rivela il guasto se  $V_a$ ,  $V_b < V_{TL}(o/p/q)$

## Esempio - soglie a $V_{DD}/2$

Lo stesso test rivela il guasto se prevale il valore alto  $(V_a > V_{DD}/2, V_b > V_{DD}/2)$

# Esempio - soglie nominali

Il test non rivela il guasto se  $V_a < V_{TL}(o/p)$ ,  $V_{TL}(p) < V_b < V_{TL}(q)$ .

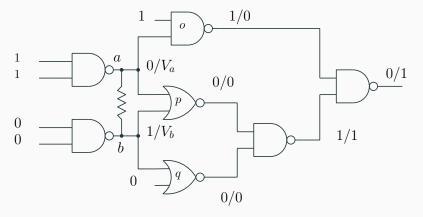

## Esempio - soglie nominali

Il guasto puó comunque dare luogo ad errori con un diverso test se  $V_a > V_{TL}(o/p), V_{TL}(p/q) < V_b$ .

### Generazione di vettori di test - II

- Un euristico efficace esplora le condizioni logiche ed elettriche che massimizzano il valore di R per cui il guasto da luogo a un errore in uscita  $(R_{max})$

- si massimizza lo sbilanciamento fra le conduttanze dei gate coinvolti

- si propagano gli effetti del guasto attraverso il gate con la soglia logica piú vicina possibile a quella del caso fault-free

#### Generazione di vettori di test - I

- Dati i parametri circuitali e un valore di resistenza, si possono utilizzare modelli mixed-level (elettrico/logico) per determinare un vettore che rivela un bridging

- Il valore di R peró non é noto

- Si cerca di generare un insieme di test che riveli il guasto per ogni valore di R che puó dare luogo a un errore in uscita

- Se rimangono intervalli di valori di *R* non rivelati dai test, questi vanno a contribuire al defect level

## Necessitá di piú vettori di test per guasto

- É possibile che siano necessari piú test anche considerando le sole condizioni nominali

- Problemi di riconvergenza logica nel fan-out dei segnali guasti possono fare in modo che un singolo test non riveli il guasto per alcuni  $R < R_{max}$

## Necessitá di piú vettori di test per guasto

- É possibile che siano necessari piú test anche considerando le sole condizioni nominali

- Problemi di riconvergenza logica nel fan-out dei segnali guasti possono fare in modo che un singolo test non riveli il guasto per alcuni  $R < R_{max}$

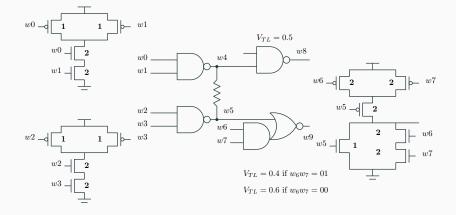

## Esempio - II

- I gate sono dimensionati in modo simmetrico

- Massimo sbilanciamento fra le conduttanze quando il NAND con uscita a 1 ha 00 in ingresso  $\rightarrow$  se R=0,  $V_x=g_{up}/(g_{down}+g_{up})=2/3V_{DD}$

- Siccome il valore alto prevale, conviene propagare il segnale che ha il valore 0 nel circuito fault-free

- Questo va fatto attraverso il gate con la soglia più bassa possibile (AOI con ingresso -10 cui corrisponde  $V_{TL} = 0.6$ )

- Per l'attivazione si ha  $w_0w_1w_2w_3 = 0011$  (cui corrispondono  $w_4 = 1$  e  $w_5 = 0$  nel caso fault-free)

- Per la propagazione si ha  $w_6w_7 = 10$

## Esempio - I

NAND

$$01 \lor 10 \quad 00 \quad 11 \quad 1 - \frac{1}{g_{up} = 1} \quad g_{up} = 2 \quad g_{down} = 1 \quad V_{TL} = 0.5$$

AOI  $01 \lor -10 \quad -00 \quad V_{TL} = 0.4V \quad V_{TL} = 0.6V$

# Variazioni dei parametri circuitali

- Le conduttanze dei gate guasti e le soglie dei gate nel fan-out sono soggette a variazioni statistiche dei parametri circuitali

- Un singolo test calcolato in condizioni nominali pu

ó non

essere in grado di rivelare il guasto per tutti i valori di R che

possono dare luogo a errori logici

- Si utilizzano piú test senza fare ipotesi su soglie e conduttanze

- Modelli semplici come il four-way bridging fault (prevale a quando é 0/1 o prevale b quando é 0/1)

- Modelli localmente esaustivi in cui si generano test che coprono tutte le possibili condizioni di attivazione e propagazione

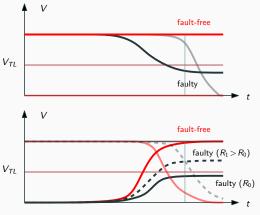

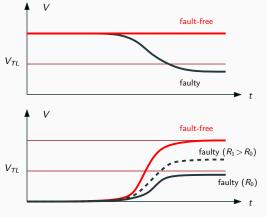

## Effetti dinamici dei bridging

- I bridging anche se non danno luogo a errori logici possono dare luogo a rilevanti effetti dinamici (ritardi addizionali)

- Un collaudo a bassa frequenza puó non rivelare tali guasti

- Alla frequenza operativa del circuito tali guasti possono dare luogo a errori logici

- Gli effetti dinamici di un bridging possono anche invalidare un test che sarebbe in grado di rivelare il guasto in condizioni statiche

## Esempi di effetti dinamici di bridging

Il ritardo addizionale con cui viene raggiunto il valore intermedio puó annullare la rivelazione del guasto

Indipendentemente dal ritardo addizionale, il guasto rivelabile staticamente rimane tale  $(R_0)$

Il guasto puó diventare rivelabile dinamicamente anche se non lo é staticamente ( $R_1$ )

# Esempi di effetti dinamici di bridging

Il ritardo addizionale con cui viene raggiunto il valore intermedio puó annullare la rivelazione del guasto

Indipendentemente dal ritardo addizionale, il guasto rivelabile staticamente rimane tale  $(R_0)$

Il guasto puó diventare rivelabile dinamicamente anche se non lo é staticamente ( $R_1$ )