### Cache L1 ed L2

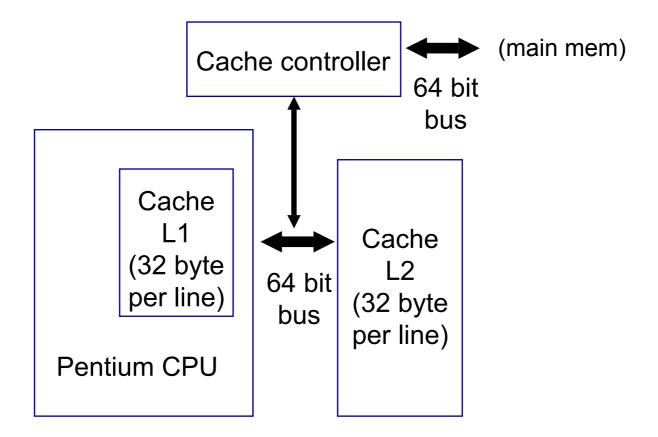

In un sistema basato sul processore Pentium, si hanno tipicamente due livelli di memoria cache:

L1: interna (on-chip)

L2: esterna (on-board)

# Esempio di cache L2

- Per descrivere l'organizzazione di una memoria cache reale, si può esaminare un esempio di cache L2 (Motorola MCM64AF2)

- Cache di 256 KB, direct mapped:

- 8 chip da 32 KB ciascuno per i dati

- 1 chip da 8KB per le tag (in realtà è da 32KB anch'esso, ma i pin A13-A14 sono fissi a 0: usato per 1/4 della sua capacità)

- Linee da 32 byte ⇒ 8192 set (256KB/32)

5 bit di index (A0-A4), 13 bit di set (A5-A17)

### Modalità di funzionamento

Le linee vengono trasferite nella/dalla cache con cicli burst: la CPU emette un solo indirizzo per 4 trasferimenti, il cache controller si occupa di accedere alle corrispondenti locazioni della cache. Durante ciascuno dei 4 trasferimenti, viene trasferito un blocco di 8 byte della linea della cache

#### Interpretazione dell'indirizzo:

- A0-A2: non servono: la memoria cache viene sempre acceduta a 8 byte per ciclo, e A0-A2 sono sempre sottintesi uguali a 000.

- A3-A4: servono per differenziare gli indirizzi dei 4 trasferimenti: xxx00000, xxx01000, xxx10000, xxx11000

- A5-A17: selezionano il set

- A18-A25: costituiscono la tag

In totale, solo 26 bit di indirizzo  $\Rightarrow$  2<sup>26</sup> = 64MB di spazio di indirizzamento coperto dalla cache

# Principali collegamenti

- i pin DQ0-DQ7delle 8 memorie dati sono collegati ordinatamente al data bus

- i pin A0-A1 delle 8 memorie dati sono collegati ai bit CA3-CA4 del cache controller (per destinare i 4 trasferimenti in locazioni diverse)

- i pin A2-A14 delle 8 memorie dati sono collegati ai bit A5-A17 dell'address bus (set)

- i pin A0-A12 della tag memory sono collegati anch'essi ai bit A5-A17 dell'address bus (c'e' una tag sola per tutti e 4 i trasferimenti)

- i pin DQ0-DQ7 della tag memory sono collegati ai bit TIO0-TIO7 del cache controller