# Segnali binari

#### M. Favalli

**Engineering Department in Ferrara**

<ロ > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 る の へ ○ </p> Segnali binari Reti logiche

Sommario

(ENDIF)

- Segnali analogici e digitali

#### Sommario

- Segnali analogici e digitali

- Segnali binari

- Segnali sincroni e asincroni

(ENDIF) Segnali binari

## Introduzione

- La maggior parte dei sistemi digitali utilizzano grandezze binarie (bit che pssono assumere i valori 0/1) per codificare le informazioni

- Questa non é l'unica alternativa possibile

- La codifica binaria delle informazioni presenta dei vantaggi dal punto di vista:

- dell'affidabitá nella trasmissione, elaborazione e memorizzazione delle informazioni

- della semplicitá ed efficienza dei blocchi logici che elaborano tali informazioni

Segnali binari

#### Segnali

- Gli elementi del supporto fisico dell'informazione e le grandezze fisiche che li caratterizzano vengono definiti come segnali

- Ciascun segnale pu

ó assumere valori all'interno di un insieme che pu

ó essere infinito (un intervallo di reali) o finito

- Nel primo caso il sistema viene definito "analogico", nel secondo "digitale"

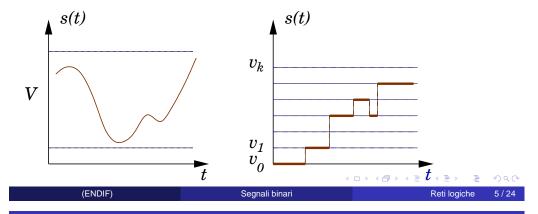

# Discretizzazione

Si tratta dell'operazione che consente di passare da un segnale analogico a uno discreto.

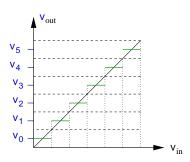

#### Funzione di discretizzazione

(ENDIF)

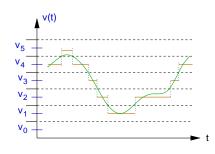

#### Esempio

## Segnali

- I segnali possono essere costituiti dalle piú diverse quantitá (forza, pressione, tensione, corrente, intensitá di flusso luminoso) e tipicamente assumono valori continui

- In prospettiva possono esistere anche segnali discreti (numero di elettroni), posizione di elettroni, spin etc.

- I segnali evolvono nel tempo dando luoo a forme d'onda

- Nel seguito, faremo riferimento a a segnali il cui valore é dato dalla tensione in una interconnessione di un circuito

(ENDIF) Segnali binari Reti logiche 6 / 24

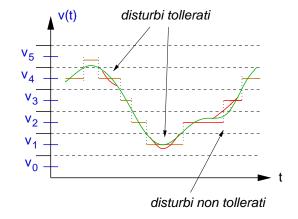

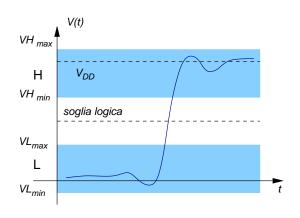

#### Disturbi

Qualsiasi sistema fisico é soggetto a disturbi che possono alterare un segnale. Nel caso di segnali digitali, gli effetti del disturbo sono limitati dall'operazione di discretizzazione che introduce un margine di tolleranza

Segnali binari

#### Sommario

- Segnali binari

|         | •              | ∢ ≣ | > ∢ ≣ >     | =  | 200  |

|---------|----------------|-----|-------------|----|------|

| (ENDIF) | Segnali binari |     | Reti logich | ne | 9/24 |

# Bit e configurazioni binarie

• I valori binari di un segnale H ed L possono essere associati a un bit  $b \in \{0, 1\}$

| Codifica ("positiva") | Codifica ("negativa") |

|-----------------------|-----------------------|

| <i>H</i> → 1          | <i>H</i> → 0          |

| $L \rightarrow 0$     | $L \rightarrow 1$     |

- Un insieme di n segnali puó assumere come valore una configurazione di *n* bit

- Esempio: configurazioni di 3 bit:

(ENDIF)

| 000 | 100 |

|-----|-----|

| 001 | 101 |

| 010 | 110 |

| 011 | 111 |

• Le configurazioni binarie sono in numero 2<sup>n</sup>

# Segnali binari

- A paritá di intervallo di variazione dei segnali, il caso in cui n=2presenta il migliore margine di immunitá ai disturbi

- Esempio nel caso in cui il segnale sia costituito da una tensione

(ENDIF) Segnali binari

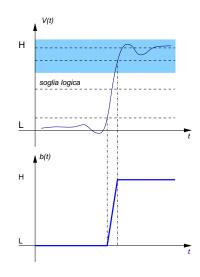

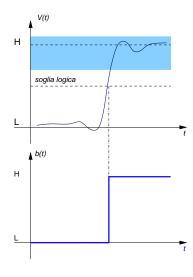

# Astrazione di forme d'onda binarie

#### Piecewise linear

(ENDIF)

## Segnali binari vs. segnali multilivello

- Se sono disponibili k livelli logici e n segnali, si hanno k<sup>n</sup> configurazioni

- Il rapporto fra il numero di configurazioni binarie e k-arie per n segnali é

$$\left(\frac{2}{k}\right)^n$$

- I segnali binari richiedono un numero molto grande di interconnessioni a paritá di informazione portata

- Esempio: se k = 10 e n = 4 possiamo rappresentare tutti i naturali da 0 a 9999, mentre se k = 2, solo quelli da 0 a 15

(ENDIF) Segnali binari Reti logiche 13/2

#### Sommario

- Segnali analogici e digitali

- Segnali binar

- Segnali sincroni e asincroni

#### Esercizi

- **1** Si calcolino le configurazioni binarie per n = 4

- ② Si considerino 3 livelli logici e n = 3; si determinino tutte le possibili configurazioni per tali parole

(ENDIF) Segnali binari Reti logiche 14/24

## Interpretazione dei segnali nel dominio del tempo

Chiaramente l'informazione viene portata da gruppi di segnali binari

Nasce il problema di determinare il valore segnali al tempo *t* ovvero di associare una configurazione binaria a tale valore

(ENDIF)

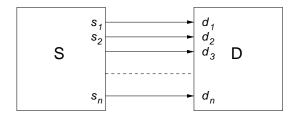

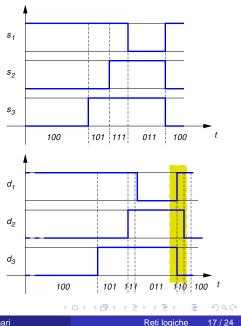

#### Interpretazione dei segnali nel dominio del tempo

- La sorgente dei segnali é connessa alla destinazione tramite interconnessioni le quali presentano un ritardo

- Tali ritardi sono difficili da controllare ⇒ é facile che i ritardi associati a segnali diversi presentino valori diversi

- Come si puó osservare la sequenza di configurazioni ricevute differisce da quella trasmessa

(ENDIF) Segnali binari Reti logiche 17 /

# Segnale di clock

Si tratta di un segnale periodico (binario) in cui un evento (fronti di salita/discesa) o un livello (alto, nell'esempio seguente) denota gli istanti o intervalli (brevi) in cui i segnali sincroni devono avere un valore costante

#### Nota

Un segnale s(t) si dice periodico con periodo T se s(t) = s(t - T)

- In conseguenza di un evento di sincronizzazione la sorgente puó variare il valore dei segnali e, se alcune condizioni sono rispettate, i segnali sono campionabili dalla destinazione

- Diversamente dal caso asincrono, la stessa configurazione puó essere trasmessa per piú istanti di sincronizzazione

## Segnali asincroni e segnali sincroni

- Nel caso precedente ogni volta che si ha un cambiamento di un segnale, si suppone di avere ricevuto una nuova configurazione

- In questo caso i segnali vengono definiti asincroni

- L'utilizzo di segnali asincroni ha alcuni vantaggi, ma presenta diversi problemi dal punto di vista della progettazione

- Si puó fare un operazione simile alla discretizzazione nel dominio dei tempi, si suppone che esistano istanti nei quali il significato dei segnali é definito correttamente lasciando i segnali liberi di cambiare al di fuori di questi intervalli di tempo

- É necessario un supporto fisico per questa operazione di sincronizzazione che é dato da uno o piú segnali di clock

(ENDIF) Segnali binari Reti logiche 18 / 24

# Segnali sincroni

- La sequenza di configurazioni ricevute é uguale a quella trasmessa nonostante il ritardo da s<sub>2</sub> a d<sub>2</sub> sia maggiore rispetto agli altri ritardi

- Tale ritardo puó avere un qualsiasi valore? Si puó campionare un segnale in qualsiasi momento?

◆□▶◆□▶◆豊▶◆豊▶ 豊 釣९()

Reti logiche 19 / 24

(ENDIF) Segnali binari

(ENDIF)

Segnali binari

Reti logiche

20 / 24

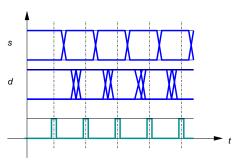

## Segnali sincroni

Le forme d'onda di piú segnali sono accorpate in una sola dando rilievo ai cambiamenti di valore della configurazione e agli intervalli di tempo in cui i segnali rimangono stabili

- Gli istanti di sincronizzazione devono corrispondere a intervalli di tempo in cui non avvengono transizioni

- Si vedrá in seguito il modo per progettare reti di questo tipo

|         |                |              | 4)40    |

|---------|----------------|--------------|---------|

| (ENDIF) | Segnali binari | Reti logiche | 21 / 24 |

|         |                |              |         |

#### Confronto

- La facilitá di progetto é il principale vantaggio dei sistemi sincroni

- Lo svantaggio é dato dalla velocitá

- ritardi delle interconnessioni nell'esempio precedente

| interc.               | ritardo |  |  |

|-----------------------|---------|--|--|

| $s_1 \rightarrow d_1$ | 0.2ns   |  |  |

| $s_2 \rightarrow d_2$ | 0.4ns   |  |  |

| $s_3 \rightarrow d_3$ | 0.3ns   |  |  |

- si supponga di voler trasmettere la sequenza di configurazioni 101,

111 e 011 a partire dalla conf. iniziale 000

- nel caso asincrono ho bisogno di 0.3ns per 101 (cambiano  $s_1$  e  $s_3$ ), 0.4ns per 111 (cambia  $s_3$ ) e 0.2ns per 011 (cambia  $s_1$ )  $\Rightarrow$  totale = 0.9ns

- nel caso sincrono il periodo di clock deve essere almeno uguale del ritardo massimo per cui per trasmettere 101, 111 e 011 impiego  $3 \cdot 0.4ns = 1.2ns$

- margini sui ritardi nominali

#### Notazione per segnali sincroni

- Nel caso di sistemi sincroni, l'attenzione puó essere focalizzata sul valore dei segnali negli istanti di sincronizzazione k=0,1,2... prescindendo dai dettagli sulle temporizzazioni

- Il valore del segnale nel k-mo periodo di clock puó essere denotato come s(k) (intendendo s(t = kT))

- Si noti che questa é un operazione di astrazione: un sistema sincrono é l'astrazione di un sistema asincrono progettato secondo determinate regole

- I valori al di fuori degli istanti di sincronizzazione non interessano

- Le convenzioni su ritardi e periodo di clock sono rispettate

⟨ENDIF⟩

Segnali binari

Reti logiche

22 / 24

#### Conclusioni

Abbiamo visto le caratteristiche dei segnali utilizzati nei sistemi digitali:

- discretizzazione dei segnali

- sistemi asincroni e sincroni

Per poter vedere le unitá in grado di elaborare tali segnali dovremo prima introdurre un adeguato modello matematico

Segnali binari

(ENDIF)