## Componenti per l'elaborazione binaria dell'informazione

Approfondimento del corso di reti logiche

#### M. Favalli

Engineering Department in Ferrara

4ロト 4回 ト 4 重 ト 4 重 ・ 夕 Q ○ M. Favalli (ENDIF) Porte logiche Sommario

- Porte logiche

- - Analisi

- Sintesi

#### **Sommario**

- Porte logiche

- Il livello switch

- Aspetti tecnologici

- Reti logiche combinatorie

- Analisi

- Sintesi

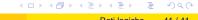

Si puó dare una definizione duplice delle porte logiche (gate):

#### Visione indipendente dalla tecnologia

Semplici funzioni dell'algebra di commutazione con le quali costruire reti logiche che realizzano funzioni più complesse

#### Visione dipendente dalla tecnologia

Circuiti elementari di tipo digitale messi a disposizione da una data tecnologia

## Porte logiche

numero di ingressi (fan-in) = 2

<ロ > < 個 > < 量 > < 量 > 量 > のQで M. Favalli (ENDIF) Gate Reti logiche

Porte logiche

# Aspetti tecnologici

- Esistono diverse tecnologie microelettroniche che consentono di realizzare gate (TTL, ECL, MOS, CMOS ....)

- Ciascuna tecnologia consente di realizzare in maniera efficiente solo un certo numero di tipi di gate (gli altri sono realizzabili mediante opportune reti di gate elementari)

- Al livello tecnologico i gate non sono caratterizzati solo dalle funzioni che realizzano, ma anche da altri parametri (costo, ritardo, consumo di potenza)

- Per capire questi aspetti analizzeremo una tecnologia in dettaglio

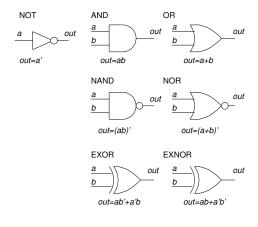

## Porte logiche

numero di ingressi (fan-in) > 2

Le porte logiche possono essere estese al caso in cui siano presenti piú ingressi

M. Favalli (ENDIF) Gate Reti logiche

Gate

Il livello switch

#### Sommario

- Il livello switch

- - Analisi

- Sintesi

8 / 41

◆□ → ◆□ → ◆ = → ◆ = → へ へ ○

#### Livello switch

- La tecnologia elettronica piú diffusa é attualmente quella CMOS

- In tale tecnologia il componente elementare più semplice descrivibile al livello logico non é il gate, ma il transistore descrivibile come un interruttore (switch)

- Questo ci consente di vedere il modo in cui una porta logica é costruita

M. Favalli (ENDIF) Gate Reti logiche 9/4

Il livello switch

# Descrizione di reti di switch mediante l'algebra di commutazione

- I sistemi fisici costituiti da switch interconnessi sono descrivibili utilizzando l'algebra di commutazione

- Bisogna codificare gli stati OFF e ON con un valore binario

| logi | ca positiva | logi | ca negativa |

|------|-------------|------|-------------|

| 0    | OFF         | 0    | ON          |

| 1    | ON          | 1    | OFF         |

Per descrizione della rete, si intende un espressione che assume il valore 1 se la rete é ON (logica positiva)

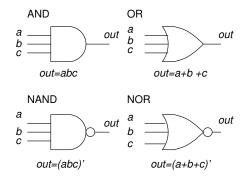

#### Livello switch

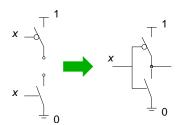

- Supponiamo che un segnale binario (x) possa controllare lo stato (ON, OFF) dell'interruttore

- Nella tecnologia CMOS sono presenti due tipi di transistori

| tipo <i>n</i> |       | tipo p |       |  |

|---------------|-------|--------|-------|--|

| X             | stato | X      | stato |  |

| 0             | OFF   | 0      | ON    |  |

| 1             | ON    | 1      | OFF   |  |

M. Favalli (ENDIF) Gate Reti logiche 10 / 41

Il livello switch

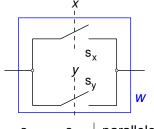

## Connessioni serie e parallelo

#### Connessione serie:

|       | <b>VV</b> |       |  |

|-------|-----------|-------|--|

| $S_X$ | $s_y$     | serie |  |

| OFF   | OFF       | OFF   |  |

| OFF   | ON        | OFF   |  |

| ON    | OFF       | OFF   |  |

| ON    | ON        | ON    |  |

#### Connessione parallelo:

| $S_X$ | $s_y$ | parallelo |

|-------|-------|-----------|

| OFF   | OFF   | OFF       |

| OFF   | ON    | ON        |

| ON    | OFF   | ON        |

| ON    | ON    | ON        |

# Rappresentazione logica

|                 | $S_X$ | $s_y$ | serie | $S_X$ | $s_y$ | parallelo |

|-----------------|-------|-------|-------|-------|-------|-----------|

|                 | 0     | 0     | 0     | 0     | 0     | 0         |

|                 | 0     | 1     | 0     | 0     | 1     | 1         |

| Logica positiva | 1     | 0     | 0     | 1     | 0     | 1         |

|                 | 1     | 1     | 1     | 1     | 1     | 1         |

|                 | AND   |       |       |     | OR    |       |           |

|-----------------|-------|-------|-------|-----|-------|-------|-----------|

|                 | $S_X$ | $s_y$ | serie |     | $S_X$ | $s_y$ | parallelo |

|                 | 1     | 1     | 1     | _   | 1     | 1     | 1         |

|                 | 1     | 0     | 1     |     | 1     | 0     | 0         |

| Logica negativa | 0     | 1     | 1     |     | 0     | 1     | 0         |

|                 | 0     | 0     | 0     |     | 0     | 0     | 0         |

|                 | '     |       |       | ,   |       |       |           |

|                 | OR    |       |       | AND |       |       |           |

|                    | •                 |              | *) Q (  |

|--------------------|-------------------|--------------|---------|

| M. Favalli (ENDIF) | Gate              | Reti logiche | 13 / 41 |

|                    |                   |              |         |

|                    | Il livello switch |              |         |

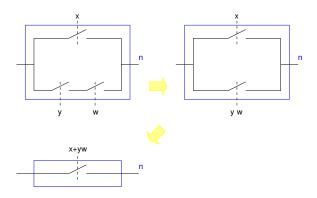

#### Reti di switch

- Reti di switch in serie e in parallelo possono essere composte in reti piú complesse

- Tali reti possono essere analizzate sostituendo iterattivamente:

- a ciascuna serie di due o più switch un singolo switch controllato dal prodotto logico degli ingressi degli switch sostituiti

- a ciascun parallelo di due o piú switch un singolo switch controllato dalla somma logica degli ingressi degli switch sostituiti

## Principio di dualitá

- Utilizzando lo stesso tipo di logica, le reti serie e parallelo realizzano funzioni duali (AND, OR)

- Cambiando tipo di logica, la stessa rete viene descritta da una funzione duale

- Il principio di dualità riguarda il modello logico dei sistemi fisici

- Punto di vista del calcolo delle proposizioni

- La serie é ON se entrambi gli switch sono ON.

- Il parallelo é ON se uno o l'altro degli switch é ON.

- La serie é OFF se uno degli switch é OFF.

- Il parallelo é OFF se entrambi gli switch sono OFF.

Si puó quindi affermare che la rete n é ON se é vera x + yw

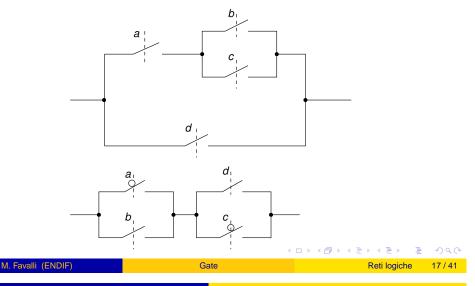

#### Esercizi di analisi

Si analizzino queste reti di switch nell'ipotesi di utilizzare una logica positiva

Il livello switch

## Gate (tecnologia CMOS)

- La soluzione consiste nel fare in modo che una rete di switch possa controllare gli switch di un altra rete (con un guadagno in grado di "rinforzare" i segnali )

- Vediamo come esempio il caso della tecnologia CMOS

- Procuriamoci le costanti 1 (vdd) e 0 (gnd) e utilizziamo switch di tipo p e n per realizzare due reti con stati complentari

| X | pull-down (n) | pull-up (p) |

|---|---------------|-------------|

| 0 | OFF           | ON          |

| 1 | ON            | OFF         |

|   |               | !           |

#### **Problema**

- Le reti di switch sono piuttosto interessanti, ma c'é un problema di carattere elettrico.

- Gli switch non sono ideali ma hanno una resistenza serie per cui l'informazione si degrada attraversando serie di con troppi switch

- Come realizzare espressioni complesse?

- Si fará riferimento alla logica positiva

|                    |                   | 4 D F 4 DF F 4 E F 4 E F 4) Q (* |

|--------------------|-------------------|----------------------------------|

| M. Favalli (ENDIF) | Gate              | Reti logiche 18 / 41             |

|                    | ****              |                                  |

|                    | Il livello switch |                                  |

|                    |                   |                                  |

| NAND               |                   |                                  |

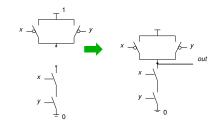

- Nella tecnologia CMOS non si puó realizzare direttamente un gate AND

- La realizzazione di un NAND é simile a quella di un NOT: si costruiscono due reti complementari

- pull-up: che pilota un 1 uno degli ingressi vale 0

- pull-down: che pilota uno 0 quando entrambi gli ingressi valgono 1

| хy | pull-down (n) | pull-up (p) |

|----|---------------|-------------|

| 00 | OFF           | ON          |

| 01 | OFF           | ON          |

| 10 | OFF           | ON          |

| 11 | ON            | OFF         |

|    |               | '           |

#### Esercizi

Si realizzino porte logiche CMOS per le seguenti funzioni logiche:

- out = (x + y)'

- out =  $(x \cdot (w + y))'$

- out = a + b

M. Favalli (ENDIF)

Aspetti tecnologici

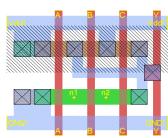

## Circuiti integrati

- Alcune informazioni sulle porte logiche che possono essere dedotte considerando la loro struttura al livello switch

- Una ulteriore informazione riguarda la tecnologia:

- i circuiti sono realizzati integrando numerose porte logiche (> 10<sup>6</sup>) in un circuito integrato realizzato con materiali semiconduttori (es. silicio)

- la tecnologia é planare: i dispositivi (switch, gate) non possono essere sovrapposti (le interconnessioni invece possono occupare diversi livelli)

- il costo é proporzionale all'area utilizzata che dipende dal numero di dispositivi e dalle interconnessioni

Sommario

- Aspetti tecnologici

- - Analisi

- Sintesi

- Nella tecnologia CMOS un gate corrisponde fisicamente a un area rettangolare le cui dimensioni sono proporzionali al numero di transistori e quindi di ingressi

- In una rete complessa, un primo contributo al costo é dato da un termine proporzionale alla somma dei gate pesata sui loro ingressi

Gate

• Si vedrá in seguito il contributo delle interconnessioni

Esempio di NAND a 3 ingressi

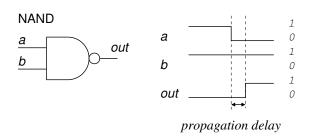

#### Ritardo

- I cambiamenti di valore degli ingressi non si riflettono istantaneamente sull'uscita

- Si ha un ritardo che é proporzionale al numero di transistori in serie che pilotano il nuovo valore

M. Favalli (ENDIF) Gate Reti logiche 25 / 41

Reti logiche combinatorie

## Reti logiche combinatorie

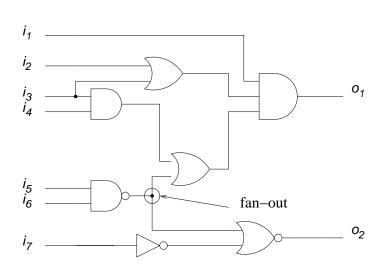

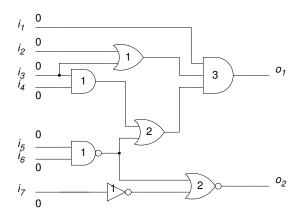

- Una rete logica consiste di un insieme di porte logiche interconnesse secondo opportune regole in modo da una relizzare una funzione  $f: \{0,1\}^n \to \{0,1\}^m$

- Siano  $i_1, i_2, ...., i_n$  gli ingressi di tale rete e  $o_1, o_2, ...., o_m$ , le sue uscite

- Regole

- gli ingressi di un gate possono essere dati da ingressi della rete, da una costante o da uscite di altri gate

- l'uscita di un gate puó essere connessa agli ingressi di un altro gate o puó pilotare un uscita

- le uscite di due gate non devono mai essere connesse insieme

- non devono esistere cammini ciclici nella rete

Porte logiche

Sommario

- 2 Il livello switch

- 3 Aspetti tecnologic

- 4 Reti logiche combinatorie

- Analisi

- Sintesi

Esempio

## Analisi e sintesi di reti combinatorie

- Per analisi di una rete combinatoria si intende il processo con il quale partendo dalla rete si ottiene la funzione corrispondente

- Per sintesi di una rete combinatoria si intende il processo con il quale partendo da una funzione e da eventuali obbiettivi di progetto (costo, ritardo) si ottiene una rete

- In entrambi i casi, le espressioni dell'algebra di commutazione sono il modello matematico che consente di gestire le trasformazioni che si hanno nei due processi

M. Favalli (ENDIF) Gate Reti logiche combinatorie Analisi Esempio di analisi

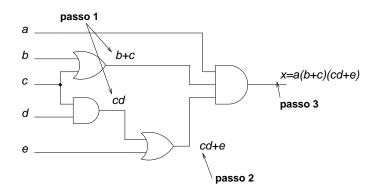

# Algoritmo di analisi

Rete logica Espressione **Funzione** algoritmo valutazione

Si assegna un nome a ciascun ingresso

Reti logiche combinatorie

- 2 Si procede in maniera iterattiva dagli ingressi del circuito esprimendo l'uscita di ciascun gate come un espressione degli ingressi della rete

- a ciascun passo vengono considerati tutti i gate i cui ingressi sono giá stati calcolati

- 3 Si procede fino a quando non si ha l'espressione di tutte le uscite della rete

- Si inseriscono nell'espressione tutte le parentesi compreso quelle rese non necessarie dalle regole dell'algebra di commutazione (senza considerare le complementazioni)

- 2 Si analizza l'espressione determinando il livello di ciascun operatore binario

- o si inizializza un indice di livello a 1 o a 0 (se tutta l'espressione é racchiusa fra parentesi)

Gate

2 si incrementa di 1 tale indice tutte le volte che si incontra una parentesi aperta e lo si decrementa di 1 tutte le volte che si incontra una parentesi chiusa

## Algoritmo di sintesi - II

- 3 Si disegnano i segnali di ingresso corrispondenti alle diverse variabili dell'espressione

- Partendo dal valore piú alto dell'indice di livello, si disegnano i simboli dei gate corrispondenti agli operatori connettendo gli opportuni segnali di ingresso a tale gate

- Nel caso una variabile di ingresso o una parentesi risultino complementate si aggiunge un invertitore

M. Favalli (ENDIF) Reti logiche combinatorie

## Il ruolo del fan-out

- É possibile che una porta logica ne piloti piú di una (fan-out > 1)

- Questo consente di ridurre il numero di porte logiche e di conseguenza il costo di una rete

- L'unico problema é un aumento del ritardo della rete

- Dal punto di vista degli algoritmi di analisi non cambia nulla

- Dal punto di vista della sintesi, invece, si hanno dei cambiamenti

- In particolare, prima del passo 3, si inseriesce un ulteriore passo di ricerca di sottoespressioni comuni (si noti che l'indice di livello puó essere diverso)

- Per il momento, questa operazione verrá svolta su basi intuitive

# Esempi di sintesi

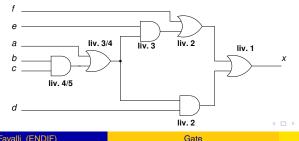

$$\begin{aligned} x &= ab + c(d + e + ac)' & x &= ab + c(d' + e)(f + g) \\ &= (a \cdot b) + (c \cdot (d + e + (a \cdot c))') & = (a \cdot b) + (c \cdot (d' + e) \cdot (f + g)) \\ &=_1 (a \cdot_2 b) +_1 (c \cdot_2 (d +_3 e +_3 (a \cdot_4 c))') & =_1 (a \cdot_2 b) +_1 (c \cdot_2 (d' +_3 e) \cdot_2 (f +_3 g)) \end{aligned}$$

M. Favalli (ENDIF

Reti logiche combinatorie

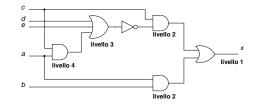

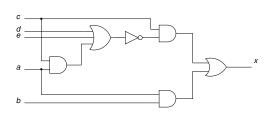

Sintesi in presenza di fan-out

$$x = (a + bc)d + ((a + bc)e + f)$$

$$= ((a + (bc))d) + (((a + (bc))e) + f)$$

$$= ((a +3 (b ·4 c)) ·2 d) +1 (((a +4 (b ·5 c)) ·3 e) +2 f)$$

Nel disegnare la rete conviene considerare la sottoespressione con i livelli maggiori

#### Livelli

#### Metodo per il calcolo dei livelli

Una rete puó essere attraversata dagli ingressi verso le uscite o viceversa (metodo precedente) assegnando a ciascun gate un indice di livello

Entrambi i tipi di indice sono utili in diverse operazioni eseguibili sulle reti.

Nel caso di attraversamento dagli ingressi (livello 0) verso le uscite, il livello di ciascun gate é definito univocamente

Nel caso di attraversamento dalle uscite (livello 0) verso gli ingressi il livello non è definito univocamente

M. Favalli (ENDIF)

Gate

Reti logiche 37/41

Reti logiche combinatorie

Sintesi

Livelli: dalle uscite verso gli ingressi

# Livelli: dagli ingressi verso le uscite

M. Favalli (ENDIF)

Gate

Reti logiche combinatorie

Sintesi

Esercizi

## Conclusioni

M. Favalli (ENDIF)

- Si é visto come si possa passare da un espressione a una rete o da una rete a un espressione a una funzione (tramite la valutazione)

- Non sappiamo ancora come passare da una funzione a un espressione

- Questo passo é quello piú rilevante dal punto di vista della sintesi